Static Public Member Functions |

Always Constructs | |

| ALWAYS_32 | ( mclk ) |

| ALWAYS_33 | ( mclk ) |

| ALWAYS_34 | ( aclk ) |

| ALWAYS_35 | ( aclk ) |

| ALWAYS_36 | ( aclk ) |

| ALWAYS_37 | ( mclk ) |

Public Attributes |

Inputs | |

| mclk | |

| aclk | |

| mrst | |

| arst | |

| cmd_ad | [ 7 : 0 ] |

| cmd_stb | |

| status_start | |

| has_burst0 | |

| data_in_chn0 | [ 31 : 0 ] |

| pre_valid_chn0 | |

| has_burst1 | |

| data_in_chn1 | [ 31 : 0 ] |

| pre_valid_chn1 | |

| has_burst2 | |

| data_in_chn2 | [ 31 : 0 ] |

| pre_valid_chn2 | |

| has_burst3 | |

| data_in_chn3 | [ 31 : 0 ] |

| pre_valid_chn3 | |

| saxi_awready | |

| saxi_wready | |

| saxi_bvalid | |

| saxi_bid | [ 5 : 0 ] |

| saxi_bresp | [ 1 : 0 ] |

Outputs | |

| status_ad | [ 7 : 0 ] |

| status_rq | |

| en_chn0 | |

| read_burst0 | |

| en_chn1 | |

| read_burst1 | |

| en_chn2 | |

| read_burst2 | |

| en_chn3 | |

| read_burst3 | |

| saxi_awaddr | [ 31 : 0 ] |

| saxi_awvalid | |

| saxi_awid | [ 5 : 0 ] |

| saxi_awlock | [ 1 : 0 ] |

| saxi_awcache | [ 3 : 0 ] |

| saxi_awprot | [ 2 : 0 ] |

| saxi_awlen | [ 3 : 0 ] |

| saxi_awsize | [ 1 : 0 ] |

| saxi_awburst | [ 1 : 0 ] |

| saxi_awqos | [ 3 : 0 ] |

| saxi_wdata | [ 31 : 0 ] |

| saxi_wvalid | |

| saxi_wid | [ 5 : 0 ] |

| saxi_wlast | |

| saxi_wstrb | [ 3 : 0 ] |

| saxi_bready | |

Parameters | |

| MULT_SAXI_ADDR | 'h730 |

| MULT_SAXI_CNTRL_ADDR | 'h738 |

| MULT_SAXI_STATUS_REG | 'h34 |

| MULT_SAXI_HALF_BRAM | 1 |

| MULT_SAXI_BSLOG0 | 4 |

| MULT_SAXI_BSLOG1 | 4 |

| MULT_SAXI_BSLOG2 | 4 |

| MULT_SAXI_BSLOG3 | 4 |

| MULT_SAXI_MASK | 'h7f8 |

| MULT_SAXI_CNTRL_MASK | 'h7fe |

| MULT_SAXI_AWCACHE | 4 'h3 |

| MULT_SAXI_ADV_WR | 4 |

| MULT_SAXI_ADV_RD | 3 |

| BRAM_A_WDTH | MULT_SAXI_HALF_BRAM?9: 10 |

| CHN_A_WDTH | BRAM_A_WDTH - 2 |

GENERATE | |

| GENERATE [454] | |

Signals | |

| wire[ 3 : 0 ] | en_chn_mclk |

| wire[ 3 : 0 ] | run_chn_mclk |

| reg[ 7 : 0 ] | mode_reg |

| wire | en_mclk |

| reg[ 3 : 0 ] | en_chn_aclk |

| wire | en_aclk |

| wire[ 3 : 0 ] | rq_wr |

| wire[ 3 : 0 ] | grant_wr |

| wire[ 4 *CHN_A_WDTH - 1 : 0 ] | wa_chn |

| wire[ 3 : 0 ] | adv_wr_done |

| wire[ 3 : 0 ] | rq_out_chn |

| wire[ 4 *CHN_A_WDTH - 1 : 0 ] | ra_chn |

| wire[ 3 : 0 ] | pre_re |

| reg | en_we_arb |

| wire | we_grant |

| wire[ 1 : 0 ] | we_cur_chn |

| wire[ 127 : 0 ] | data_in |

| wire[ 3 : 0 ] | pre_valid |

| reg[ 3 : 0 ] | valid |

| reg[BRAM_A_WDTH - 1 : 0 ] | buf_wa |

| reg[ 31 : 0 ] | buf_wd |

| reg | buf_we |

| wire[ 3 : 0 ] | grant_rd |

| wire | grant_rd_any |

| wire | en_out_arb |

| wire[ 1 : 0 ] | re_cur_chn |

| reg[BRAM_A_WDTH - 1 : 0 ] | buf_ra |

| wire[ 31 : 0 ] | inter_buf_data |

| reg[ 2 : 0 ] | buf_re |

| wire | fifo_half_full |

| wire | fifo_nempty |

| wire[ 3 : 0 ] | wdata_busy_chn |

| wire[ 3 : 0 ] | first_re |

| wire[ 3 : 0 ] | last_re |

| wire[ 3 : 0 ] | cmd_a |

| wire[ 31 : 0 ] | cmd_data |

| wire | we_ctrl |

| wire | cmd_we_sa_len |

| wire | pre_pre_buf_we |

| reg | pre_buf_we |

| reg[ 1 : 0 ] | chn_wr |

| reg[ 1 : 0 ] | chn_rd |

| reg[ 1 : 0 ] | chn_rd_data |

| reg | pre_first_rd_valid |

| reg[ 1 : 0 ] | is_last_rd |

| wire[ 1 : 0 ] | chn_fifo_out |

| wire | axi_ptr_busy |

| wire[ 29 : 0 ] | axi_addr |

| wire[ 3 : 0 ] | axi_len |

| wire[ 29 : 0 ] | pntr_wd |

| wire[ 1 : 0 ] | pntr_wa |

| wire | pntr_we |

| reg | awvalid |

| reg[ 2 : 0 ] | aw_seq |

| reg[ 1 : 0 ] | chn_out |

| wire | fifo_re |

| reg[ 29 : 0 ] | status_pntr0 |

| reg[ 29 : 0 ] | status_pntr1 |

| reg[ 29 : 0 ] | status_pntr2 |

| reg[ 29 : 0 ] | status_pntr3 |

| wire | pntr_we_mclk |

| wire[ 128 : 0 ] | status_data |

| reg | status_tgl |

Detailed Description

Definition at line 44 of file mult_saxi_wr.v.

Member Function Documentation

|

Always Construct |

Definition at line 184 of file mult_saxi_wr.v.

|

Always Construct |

Definition at line 311 of file mult_saxi_wr.v.

|

Always Construct |

Definition at line 338 of file mult_saxi_wr.v.

|

Always Construct |

Definition at line 412 of file mult_saxi_wr.v.

|

Always Construct |

Definition at line 436 of file mult_saxi_wr.v.

|

Always Construct |

Definition at line 523 of file mult_saxi_wr.v.

Member Data Documentation

|

Parameter |

Definition at line 45 of file mult_saxi_wr.v.

|

Parameter |

Definition at line 46 of file mult_saxi_wr.v.

|

Parameter |

Definition at line 47 of file mult_saxi_wr.v.

|

Parameter |

Definition at line 48 of file mult_saxi_wr.v.

|

Parameter |

Definition at line 49 of file mult_saxi_wr.v.

|

Parameter |

Definition at line 50 of file mult_saxi_wr.v.

|

Parameter |

Definition at line 51 of file mult_saxi_wr.v.

|

Parameter |

Definition at line 52 of file mult_saxi_wr.v.

|

Parameter |

Definition at line 53 of file mult_saxi_wr.v.

|

Parameter |

Definition at line 54 of file mult_saxi_wr.v.

|

Parameter |

Definition at line 55 of file mult_saxi_wr.v.

|

Parameter |

Definition at line 56 of file mult_saxi_wr.v.

|

Parameter |

Definition at line 57 of file mult_saxi_wr.v.

|

Input |

Definition at line 61 of file mult_saxi_wr.v.

|

Input |

Definition at line 62 of file mult_saxi_wr.v.

|

Input |

Definition at line 63 of file mult_saxi_wr.v.

|

Input |

Definition at line 64 of file mult_saxi_wr.v.

|

Input |

Definition at line 66 of file mult_saxi_wr.v.

|

Input |

Definition at line 67 of file mult_saxi_wr.v.

|

Output |

Definition at line 68 of file mult_saxi_wr.v.

|

Output |

Definition at line 69 of file mult_saxi_wr.v.

|

Input |

Definition at line 70 of file mult_saxi_wr.v.

|

Output |

Definition at line 72 of file mult_saxi_wr.v.

|

Input |

Definition at line 73 of file mult_saxi_wr.v.

|

Output |

Definition at line 74 of file mult_saxi_wr.v.

|

Input |

Definition at line 75 of file mult_saxi_wr.v.

|

Input |

Definition at line 76 of file mult_saxi_wr.v.

|

Output |

Definition at line 78 of file mult_saxi_wr.v.

|

Input |

Definition at line 79 of file mult_saxi_wr.v.

|

Output |

Definition at line 80 of file mult_saxi_wr.v.

|

Input |

Definition at line 81 of file mult_saxi_wr.v.

|

Input |

Definition at line 82 of file mult_saxi_wr.v.

|

Output |

Definition at line 84 of file mult_saxi_wr.v.

|

Input |

Definition at line 85 of file mult_saxi_wr.v.

|

Output |

Definition at line 86 of file mult_saxi_wr.v.

|

Input |

Definition at line 87 of file mult_saxi_wr.v.

|

Input |

Definition at line 88 of file mult_saxi_wr.v.

|

Output |

Definition at line 90 of file mult_saxi_wr.v.

|

Input |

Definition at line 91 of file mult_saxi_wr.v.

|

Output |

Definition at line 92 of file mult_saxi_wr.v.

|

Input |

Definition at line 93 of file mult_saxi_wr.v.

|

Input |

Definition at line 94 of file mult_saxi_wr.v.

|

Output |

Definition at line 98 of file mult_saxi_wr.v.

|

Output |

Definition at line 99 of file mult_saxi_wr.v.

|

Input |

Definition at line 100 of file mult_saxi_wr.v.

|

Output |

Definition at line 101 of file mult_saxi_wr.v.

|

Output |

Definition at line 102 of file mult_saxi_wr.v.

|

Output |

Definition at line 103 of file mult_saxi_wr.v.

|

Output |

Definition at line 104 of file mult_saxi_wr.v.

|

Output |

Definition at line 105 of file mult_saxi_wr.v.

|

Output |

Definition at line 106 of file mult_saxi_wr.v.

|

Output |

Definition at line 107 of file mult_saxi_wr.v.

|

Output |

Definition at line 108 of file mult_saxi_wr.v.

|

Output |

Definition at line 110 of file mult_saxi_wr.v.

|

Output |

Definition at line 111 of file mult_saxi_wr.v.

|

Input |

Definition at line 112 of file mult_saxi_wr.v.

|

Output |

Definition at line 113 of file mult_saxi_wr.v.

|

Output |

Definition at line 114 of file mult_saxi_wr.v.

|

Output |

Definition at line 115 of file mult_saxi_wr.v.

|

Input |

Definition at line 117 of file mult_saxi_wr.v.

|

Output |

Definition at line 118 of file mult_saxi_wr.v.

|

Input |

Definition at line 119 of file mult_saxi_wr.v.

|

Input |

Definition at line 120 of file mult_saxi_wr.v.

|

Parameter |

Definition at line 125 of file mult_saxi_wr.v.

|

Parameter |

Definition at line 126 of file mult_saxi_wr.v.

|

Signal |

Definition at line 128 of file mult_saxi_wr.v.

|

Signal |

Definition at line 129 of file mult_saxi_wr.v.

|

Signal |

Definition at line 130 of file mult_saxi_wr.v.

|

Signal |

Definition at line 131 of file mult_saxi_wr.v.

|

Signal |

Definition at line 132 of file mult_saxi_wr.v.

|

Signal |

Definition at line 133 of file mult_saxi_wr.v.

|

Signal |

Definition at line 134 of file mult_saxi_wr.v.

|

Signal |

Definition at line 135 of file mult_saxi_wr.v.

|

Signal |

Definition at line 136 of file mult_saxi_wr.v.

|

Signal |

Definition at line 137 of file mult_saxi_wr.v.

|

Signal |

Definition at line 138 of file mult_saxi_wr.v.

|

Signal |

Definition at line 139 of file mult_saxi_wr.v.

|

Signal |

Definition at line 140 of file mult_saxi_wr.v.

|

Signal |

Definition at line 142 of file mult_saxi_wr.v.

|

Signal |

Definition at line 143 of file mult_saxi_wr.v.

|

Signal |

Definition at line 144 of file mult_saxi_wr.v.

|

Signal |

Definition at line 145 of file mult_saxi_wr.v.

|

Signal |

Definition at line 146 of file mult_saxi_wr.v.

|

Signal |

Definition at line 147 of file mult_saxi_wr.v.

|

Signal |

Definition at line 148 of file mult_saxi_wr.v.

|

Signal |

Definition at line 149 of file mult_saxi_wr.v.

|

Signal |

Definition at line 150 of file mult_saxi_wr.v.

|

Signal |

Definition at line 152 of file mult_saxi_wr.v.

|

Signal |

Definition at line 153 of file mult_saxi_wr.v.

|

Signal |

Definition at line 154 of file mult_saxi_wr.v.

|

Signal |

Definition at line 155 of file mult_saxi_wr.v.

|

Signal |

Definition at line 157 of file mult_saxi_wr.v.

|

Signal |

Definition at line 158 of file mult_saxi_wr.v.

|

Signal |

Definition at line 159 of file mult_saxi_wr.v.

|

Signal |

Definition at line 161 of file mult_saxi_wr.v.

|

Signal |

Definition at line 162 of file mult_saxi_wr.v.

|

Signal |

Definition at line 163 of file mult_saxi_wr.v.

|

Signal |

Definition at line 164 of file mult_saxi_wr.v.

|

Signal |

Definition at line 165 of file mult_saxi_wr.v.

|

Signal |

Definition at line 167 of file mult_saxi_wr.v.

|

Signal |

Definition at line 168 of file mult_saxi_wr.v.

|

Signal |

Definition at line 170 of file mult_saxi_wr.v.

|

Signal |

Definition at line 171 of file mult_saxi_wr.v.

|

Signal |

Definition at line 307 of file mult_saxi_wr.v.

|

Signal |

Definition at line 308 of file mult_saxi_wr.v.

|

Signal |

Definition at line 309 of file mult_saxi_wr.v.

|

Signal |

Definition at line 331 of file mult_saxi_wr.v.

|

Signal |

Definition at line 332 of file mult_saxi_wr.v.

|

Signal |

Definition at line 333 of file mult_saxi_wr.v.

|

Signal |

Definition at line 334 of file mult_saxi_wr.v.

|

Signal |

Definition at line 335 of file mult_saxi_wr.v.

|

Signal |

Definition at line 366 of file mult_saxi_wr.v.

|

Signal |

Definition at line 367 of file mult_saxi_wr.v.

|

Signal |

Definition at line 368 of file mult_saxi_wr.v.

|

Signal |

Definition at line 381 of file mult_saxi_wr.v.

|

Signal |

Definition at line 382 of file mult_saxi_wr.v.

|

Signal |

Definition at line 383 of file mult_saxi_wr.v.

|

Signal |

Definition at line 408 of file mult_saxi_wr.v.

|

Signal |

Definition at line 409 of file mult_saxi_wr.v.

|

Signal |

Definition at line 411 of file mult_saxi_wr.v.

|

Signal |

Definition at line 426 of file mult_saxi_wr.v.

|

Signal |

Definition at line 515 of file mult_saxi_wr.v.

|

Signal |

Definition at line 516 of file mult_saxi_wr.v.

|

Signal |

Definition at line 517 of file mult_saxi_wr.v.

|

Signal |

Definition at line 518 of file mult_saxi_wr.v.

|

Signal |

Definition at line 519 of file mult_saxi_wr.v.

|

Signal |

Definition at line 520 of file mult_saxi_wr.v.

|

Signal |

Definition at line 521 of file mult_saxi_wr.v.

|

Module Instance |

Definition at line 493 of file mult_saxi_wr.v.

|

Module Instance |

Definition at line 439 of file mult_saxi_wr.v.

|

GENERATE |

Definition at line 454 of file mult_saxi_wr.v.

|

Module Instance |

Definition at line 191 of file mult_saxi_wr.v.

|

Module Instance |

Definition at line 217 of file mult_saxi_wr.v.

|

Module Instance |

Definition at line 242 of file mult_saxi_wr.v.

|

Module Instance |

Definition at line 267 of file mult_saxi_wr.v.

|

Module Instance |

Definition at line 385 of file mult_saxi_wr.v.

|

Module Instance |

Definition at line 533 of file mult_saxi_wr.v.

|

Module Instance |

Definition at line 456 of file mult_saxi_wr.v.

|

Module Instance |

Definition at line 474 of file mult_saxi_wr.v.

|

Module Instance |

Definition at line 293 of file mult_saxi_wr.v.

|

Module Instance |

Definition at line 352 of file mult_saxi_wr.v.

|

Module Instance |

Definition at line 535 of file mult_saxi_wr.v.

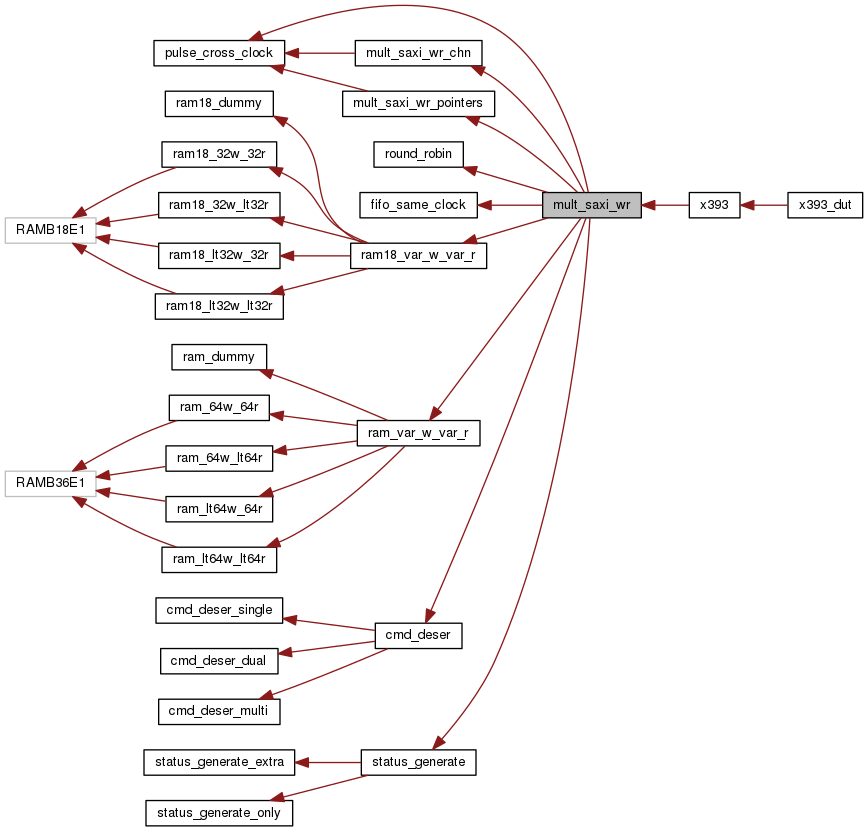

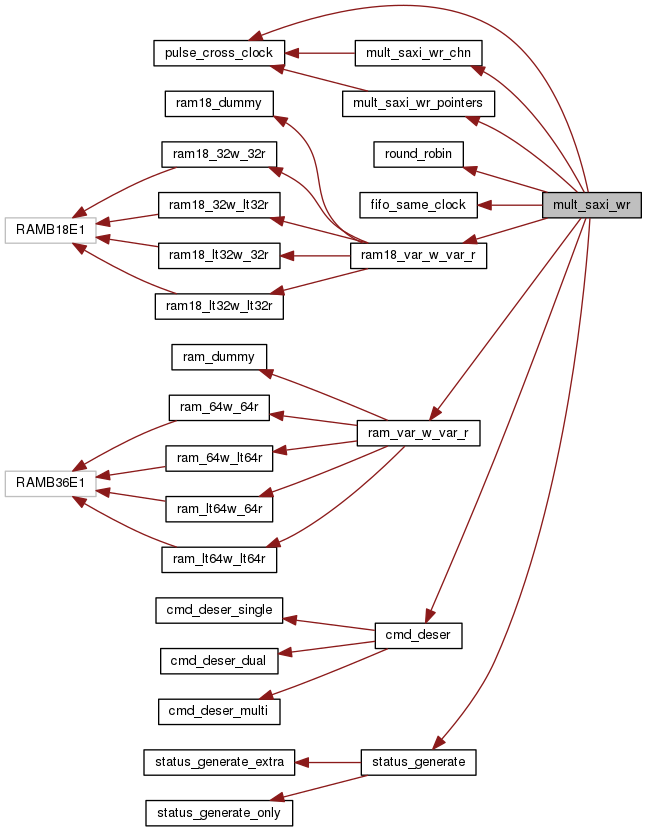

The documentation for this Module was generated from the following files:

- axi/mult_saxi_wr.v