Static Public Member Functions |

Always Constructs | |

| ALWAYS_40 | ( mclk ) |

| ALWAYS_41 | ( mclk ) |

| ALWAYS_42 | ( aclk ) |

| ALWAYS_43 | ( aclk ) |

| ALWAYS_44 | ( aclk ) |

Public Attributes |

Inputs | |

| mclk | |

| aclk | |

| chn_en_mclk | [ 3 : 0 ] |

| sa_len_di | [ 29 : 0 ] |

| sa_len_wa | [ 2 : 0 ] |

| sa_len_we | |

| chn | [ 1 : 0 ] |

| start | |

Outputs | |

| busy | |

| axi_addr | reg [ 29 : 0 ] |

| axi_len | reg [ 3 : 0 ] |

| pntr_wd | [ 29 : 0 ] |

| pntr_wa | [ 1 : 0 ] |

| pntr_we | |

Parameters | |

| MULT_SAXI_BSLOG0 | 4 |

| MULT_SAXI_BSLOG1 | 4 |

| MULT_SAXI_BSLOG2 | 4 |

| MULT_SAXI_BSLOG3 | 4 |

Signals | |

| reg[ 3 : 0 ] | chn_en_mclk_r |

| reg[ 3 : 0 ] | chn_en_aclk |

| wire | rst |

| wire | rst_aclk |

| wire[ 3 : 0 ] | chn_wr_mclk |

| wire[ 3 : 0 ] | rst_pntr_mclk |

| wire[ 3 : 0 ] | rst_pntr_aclk |

| wire | start_resetting_w |

| reg[ 1 : 0 ] | resetting |

| reg | busy_r |

| reg[ 3 : 0 ] | reset_rq |

| reg[ 3 : 0 ] | reset_rq_pri |

| wire[ 1 : 0 ] | reset_rq_enc |

| wire | en_aclk |

| reg[ 1 : 0 ] | chn_r |

| reg[ 1 : 0 ] | seq |

| wire[ 29 : 0 ] | sa_len_ram_out |

| wire[ 29 : 0 ] | ptr_ram_out |

| wire[ 2 : 0 ] | sa_len_ra |

| reg | ptr_we |

| reg[ 29 : 0 ] | ptr_inc |

| reg[ 30 : 0 ] | ptr_rollover |

| reg[ 4 : 0 ] | burst_size |

| wire[ 29 : 0 ] | ptr_wd |

| reg[ 29 : 0 ] | sa_len_ram [ 0 : 7 ] |

| reg[ 29 : 0 ] | ptr_ram [ 0 : 3 ] |

Module Instances | |

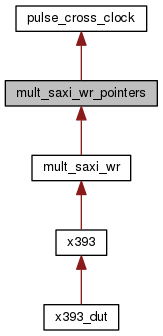

| pulse_cross_clock::rst_pntr_aclk0_i | Module pulse_cross_clock |

| pulse_cross_clock::rst_pntr_aclk1_i | Module pulse_cross_clock |

| pulse_cross_clock::rst_pntr_aclk2_i | Module pulse_cross_clock |

| pulse_cross_clock::rst_pntr_aclk3_i | Module pulse_cross_clock |

Detailed Description

Definition at line 41 of file mult_saxi_wr_pointers.v.

Member Function Documentation

|

Always Construct |

Definition at line 102 of file mult_saxi_wr_pointers.v.

|

Always Construct |

Definition at line 108 of file mult_saxi_wr_pointers.v.

|

Always Construct |

Definition at line 115 of file mult_saxi_wr_pointers.v.

|

Always Construct |

Definition at line 120 of file mult_saxi_wr_pointers.v.

|

Always Construct |

Definition at line 127 of file mult_saxi_wr_pointers.v.

Member Data Documentation

|

Parameter |

Definition at line 42 of file mult_saxi_wr_pointers.v.

|

Parameter |

Definition at line 43 of file mult_saxi_wr_pointers.v.

|

Parameter |

Definition at line 44 of file mult_saxi_wr_pointers.v.

|

Parameter |

Definition at line 45 of file mult_saxi_wr_pointers.v.

|

Input |

Definition at line 47 of file mult_saxi_wr_pointers.v.

|

Input |

Definition at line 48 of file mult_saxi_wr_pointers.v.

|

Input |

Definition at line 49 of file mult_saxi_wr_pointers.v.

|

Input |

Definition at line 50 of file mult_saxi_wr_pointers.v.

|

Input |

Definition at line 51 of file mult_saxi_wr_pointers.v.

|

Input |

Definition at line 52 of file mult_saxi_wr_pointers.v.

|

Input |

Definition at line 53 of file mult_saxi_wr_pointers.v.

|

Input |

Definition at line 54 of file mult_saxi_wr_pointers.v.

|

Output |

Definition at line 55 of file mult_saxi_wr_pointers.v.

|

Output |

Definition at line 57 of file mult_saxi_wr_pointers.v.

|

Output |

Definition at line 58 of file mult_saxi_wr_pointers.v.

|

Output |

Definition at line 61 of file mult_saxi_wr_pointers.v.

|

Output |

Definition at line 62 of file mult_saxi_wr_pointers.v.

|

Output |

Definition at line 63 of file mult_saxi_wr_pointers.v.

|

Signal |

Definition at line 65 of file mult_saxi_wr_pointers.v.

|

Signal |

Definition at line 66 of file mult_saxi_wr_pointers.v.

|

Signal |

Definition at line 67 of file mult_saxi_wr_pointers.v.

|

Signal |

Definition at line 68 of file mult_saxi_wr_pointers.v.

|

Signal |

Definition at line 69 of file mult_saxi_wr_pointers.v.

|

Signal |

Definition at line 70 of file mult_saxi_wr_pointers.v.

|

Signal |

Definition at line 71 of file mult_saxi_wr_pointers.v.

|

Signal |

Definition at line 72 of file mult_saxi_wr_pointers.v.

|

Signal |

Definition at line 73 of file mult_saxi_wr_pointers.v.

|

Signal |

Definition at line 74 of file mult_saxi_wr_pointers.v.

|

Signal |

Definition at line 75 of file mult_saxi_wr_pointers.v.

|

Signal |

Definition at line 76 of file mult_saxi_wr_pointers.v.

|

Signal |

Definition at line 77 of file mult_saxi_wr_pointers.v.

|

Signal |

Definition at line 78 of file mult_saxi_wr_pointers.v.

|

Signal |

Definition at line 79 of file mult_saxi_wr_pointers.v.

|

Signal |

Definition at line 80 of file mult_saxi_wr_pointers.v.

|

Signal |

Definition at line 81 of file mult_saxi_wr_pointers.v.

|

Signal |

Definition at line 82 of file mult_saxi_wr_pointers.v.

|

Signal |

Definition at line 83 of file mult_saxi_wr_pointers.v.

|

Signal |

Definition at line 84 of file mult_saxi_wr_pointers.v.

|

Signal |

Definition at line 85 of file mult_saxi_wr_pointers.v.

|

Signal |

Definition at line 86 of file mult_saxi_wr_pointers.v.

|

Signal |

Definition at line 87 of file mult_saxi_wr_pointers.v.

|

Signal |

Definition at line 88 of file mult_saxi_wr_pointers.v.

|

Signal |

Definition at line 107 of file mult_saxi_wr_pointers.v.

|

Signal |

Definition at line 114 of file mult_saxi_wr_pointers.v.

|

Module Instance |

Definition at line 165 of file mult_saxi_wr_pointers.v.

|

Module Instance |

Definition at line 166 of file mult_saxi_wr_pointers.v.

|

Module Instance |

Definition at line 167 of file mult_saxi_wr_pointers.v.

|

Module Instance |

Definition at line 168 of file mult_saxi_wr_pointers.v.

The documentation for this Module was generated from the following files: