Static Public Member Functions |

Always Constructs | |

| ALWAYS_398 | ( pclk ) |

| ALWAYS_399 | ( pclk ) |

| ALWAYS_400 | ( pclk ) |

| ALWAYS_401 | ( oclk ) |

| ALWAYS_402 | ( oclk ) |

| ALWAYS_403 | ( oclk ) |

Public Attributes |

Inputs | |

| pclk | |

| rst | |

| pxd | [ 11 : 0 ] |

| vact | |

| hact_in | |

Outputs | |

| lane_p | [ 3 : 0 ] |

| lane_n | [ 3 : 0 ] |

| clk_p | |

| clk_n | |

Parameters | |

| FULL_HEIGHT | 0 |

| CLOCK_MPY | 10 |

| CLOCK_DIV | 3 |

| LANE0_DLY | 1 . 3 |

| LANE1_DLY | 2 . 7 |

| LANE2_DLY | 0 . 2 |

| LANE3_DLY | 1 . 8 |

| CLK_DLY | 2 . 3 |

| EMBED_LINES | 2 |

| MSB_FIRST | 0 |

| FIFO_LOGDEPTH | 12 |

| FIFO_DEPTH | 1 << FIFO_LOGDEPTH |

| SYNC_SOF | [ 3 : 0 ] 3 |

| SYNC_SOL | [ 3 : 0 ] 1 |

| SYNC_EOF | [ 3 : 0 ] 7 |

| SYNC_EOL | [ 3 : 0 ] 6 |

GENERATE | |

| GENERATE [191] | |

Signals | |

| integer | lines_left |

| integer | pre_lines |

| reg[ 1 : 0 ] | lane_pcntr |

| wire | hact |

| reg | image_lines |

| reg | vact_d |

| reg[ 47 : 0 ] | pxd_d |

| reg[ 48 : 0 ] | fifo_di |

| reg | fifo_we |

| reg | hact_d |

| reg | next_sof |

| reg | next_line_pclk |

| reg | next_frame_pclk |

| wire | pre_fifo_we_eof_w |

| wire | pre_fifo_we_sof_sol_w |

| wire | pre_fifo_we_data_w |

| wire | pre_fifo_we_w |

| reg[ 48 : 0 ] | fifo_ram [ 0 :FIFO_DEPTH - 1 ] |

| reg[FIFO_LOGDEPTH - 1 : 0 ] | fifo_wa |

| wire | oclk |

| wire | next_line_oclk |

| wire | next_frame_oclk |

| reg | orst_r |

| wire | orst |

| wire[ 3 : 0 ] | rdy |

| wire[ 3 : 0 ] | sdata |

| wire[ 3 : 0 ] | sdata_dly |

| reg[FIFO_LOGDEPTH - 1 : 0 ] | fifo_ra |

| wire[ 48 : 0 ] | fifo_out |

| wire | fifo_dav |

| wire | sof_sol_sent |

| reg[ 1 : 0 ] | lines_available |

| wire | line_available |

| reg[ 1 : 0 ] | frames_open |

| wire | eof_sent |

| reg | clk_pn |

| wire | clk_pn_dly |

Detailed Description

Definition at line 41 of file par12_hispi_psp4l.v.

Member Function Documentation

|

Always Construct |

Definition at line 91 of file par12_hispi_psp4l.v.

|

Always Construct |

Definition at line 96 of file par12_hispi_psp4l.v.

|

Always Construct |

Definition at line 131 of file par12_hispi_psp4l.v.

|

Always Construct |

Definition at line 177 of file par12_hispi_psp4l.v.

|

Always Construct |

Definition at line 217 of file par12_hispi_psp4l.v.

|

Always Construct |

Definition at line 266 of file par12_hispi_psp4l.v.

Member Data Documentation

|

Parameter |

Definition at line 42 of file par12_hispi_psp4l.v.

|

Parameter |

Definition at line 43 of file par12_hispi_psp4l.v.

|

Parameter |

Definition at line 44 of file par12_hispi_psp4l.v.

|

Parameter |

Definition at line 45 of file par12_hispi_psp4l.v.

|

Parameter |

Definition at line 46 of file par12_hispi_psp4l.v.

|

Parameter |

Definition at line 47 of file par12_hispi_psp4l.v.

|

Parameter |

Definition at line 48 of file par12_hispi_psp4l.v.

|

Parameter |

Definition at line 49 of file par12_hispi_psp4l.v.

|

Parameter |

Definition at line 50 of file par12_hispi_psp4l.v.

|

Parameter |

Definition at line 51 of file par12_hispi_psp4l.v.

|

Parameter |

Definition at line 52 of file par12_hispi_psp4l.v.

|

Input |

Definition at line 54 of file par12_hispi_psp4l.v.

|

Input |

Definition at line 55 of file par12_hispi_psp4l.v.

|

Input |

Definition at line 56 of file par12_hispi_psp4l.v.

|

Input |

Definition at line 57 of file par12_hispi_psp4l.v.

|

Input |

Definition at line 58 of file par12_hispi_psp4l.v.

|

Output |

Definition at line 59 of file par12_hispi_psp4l.v.

|

Output |

Definition at line 60 of file par12_hispi_psp4l.v.

|

Output |

Definition at line 61 of file par12_hispi_psp4l.v.

|

Output |

Definition at line 62 of file par12_hispi_psp4l.v.

|

Parameter |

Definition at line 64 of file par12_hispi_psp4l.v.

|

Parameter |

Definition at line 65 of file par12_hispi_psp4l.v.

|

Parameter |

Definition at line 66 of file par12_hispi_psp4l.v.

|

Parameter |

Definition at line 67 of file par12_hispi_psp4l.v.

|

Parameter |

Definition at line 68 of file par12_hispi_psp4l.v.

|

Signal |

Definition at line 71 of file par12_hispi_psp4l.v.

|

Signal |

Definition at line 72 of file par12_hispi_psp4l.v.

|

Signal |

Definition at line 73 of file par12_hispi_psp4l.v.

|

Signal |

Definition at line 74 of file par12_hispi_psp4l.v.

|

Signal |

Definition at line 75 of file par12_hispi_psp4l.v.

|

Signal |

Definition at line 76 of file par12_hispi_psp4l.v.

|

Signal |

Definition at line 77 of file par12_hispi_psp4l.v.

|

Signal |

Definition at line 78 of file par12_hispi_psp4l.v.

|

Signal |

Definition at line 79 of file par12_hispi_psp4l.v.

|

Signal |

Definition at line 80 of file par12_hispi_psp4l.v.

|

Signal |

Definition at line 81 of file par12_hispi_psp4l.v.

|

Signal |

Definition at line 82 of file par12_hispi_psp4l.v.

|

Signal |

Definition at line 83 of file par12_hispi_psp4l.v.

|

Signal |

Definition at line 84 of file par12_hispi_psp4l.v.

|

Signal |

Definition at line 86 of file par12_hispi_psp4l.v.

|

Signal |

Definition at line 88 of file par12_hispi_psp4l.v.

|

Signal |

Definition at line 89 of file par12_hispi_psp4l.v.

|

Signal |

Definition at line 128 of file par12_hispi_psp4l.v.

|

Signal |

Definition at line 129 of file par12_hispi_psp4l.v.

|

Signal |

Definition at line 139 of file par12_hispi_psp4l.v.

|

Signal |

Definition at line 141 of file par12_hispi_psp4l.v.

|

Signal |

Definition at line 142 of file par12_hispi_psp4l.v.

|

Signal |

Definition at line 143 of file par12_hispi_psp4l.v.

|

Signal |

Definition at line 144 of file par12_hispi_psp4l.v.

|

Signal |

Definition at line 181 of file par12_hispi_psp4l.v.

|

Signal |

Definition at line 182 of file par12_hispi_psp4l.v.

|

Signal |

Definition at line 183 of file par12_hispi_psp4l.v.

|

Signal |

Definition at line 184 of file par12_hispi_psp4l.v.

|

Signal |

Definition at line 185 of file par12_hispi_psp4l.v.

|

Signal |

Definition at line 186 of file par12_hispi_psp4l.v.

|

Signal |

Definition at line 188 of file par12_hispi_psp4l.v.

|

Signal |

Definition at line 189 of file par12_hispi_psp4l.v.

|

Signal |

Definition at line 190 of file par12_hispi_psp4l.v.

|

Signal |

Definition at line 214 of file par12_hispi_psp4l.v.

|

Signal |

Definition at line 215 of file par12_hispi_psp4l.v.

|

Signal |

Definition at line 264 of file par12_hispi_psp4l.v.

|

Signal |

Definition at line 265 of file par12_hispi_psp4l.v.

|

GENERATE |

Definition at line 191 of file par12_hispi_psp4l.v.

|

Module Instance |

Definition at line 194 of file par12_hispi_psp4l.v.

|

Module Instance |

Definition at line 155 of file par12_hispi_psp4l.v.

|

Module Instance |

Definition at line 166 of file par12_hispi_psp4l.v.

|

Module Instance |

Definition at line 231 of file par12_hispi_psp4l.v.

|

Module Instance |

Definition at line 240 of file par12_hispi_psp4l.v.

|

Module Instance |

Definition at line 248 of file par12_hispi_psp4l.v.

|

Module Instance |

Definition at line 256 of file par12_hispi_psp4l.v.

|

Module Instance |

Definition at line 271 of file par12_hispi_psp4l.v.

|

Module Instance |

Definition at line 145 of file par12_hispi_psp4l.v.

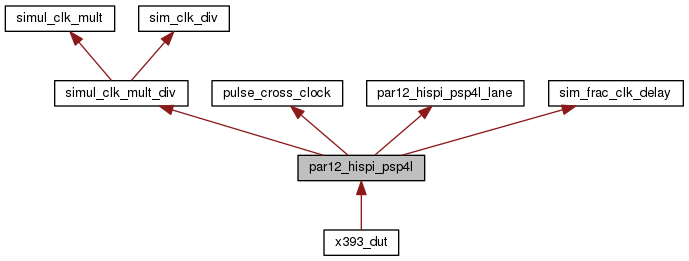

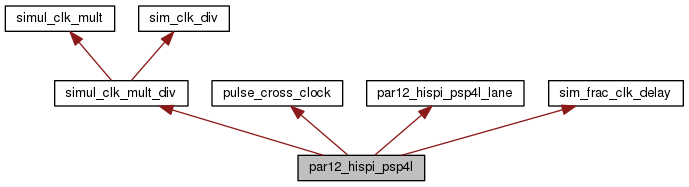

The documentation for this Module was generated from the following files:

- simulation_modules/par12_hispi_psp4l.v