Static Public Member Functions |

Always Constructs | |

| ALWAYS_404 | ( clk ) |

Public Attributes |

Inputs | |

| clk | |

| rst | |

| din | [ 12 : 0 ] |

| dav | |

| next_line | |

Outputs | |

| sof_sol_sent | reg |

| rdy | |

| sout | reg |

Parameters | |

| SYNC_SOF | [ 3 : 0 ] 3 |

| SYNC_SOL | [ 3 : 0 ] 1 |

| SYNC_EOF | [ 3 : 0 ] 7 |

| SYNC_EOL | [ 3 : 0 ] 6 |

| IDL | [ 11 : 0 ] 12 'h800 |

| MSB_FIRST | 0 |

Signals | |

| reg[ 11 : 0 ] | sr |

| reg[ 11 : 0 ] | sr_in |

| reg | sr_in_av |

| reg[ 3 : 0 ] | bcntr |

| reg[ 3 : 0 ] | seq_sof |

| reg[ 3 : 0 ] | seq_eof |

| reg[ 7 : 0 ] | seq_eol_sol |

| reg | embed |

| wire | dav_rdy |

| wire | is_sync |

| wire[ 11 : 0 ] | din_filt |

| wire | pause |

Detailed Description

Definition at line 288 of file par12_hispi_psp4l.v.

Member Function Documentation

|

Always Construct |

Definition at line 320 of file par12_hispi_psp4l.v.

Member Data Documentation

|

Parameter |

Definition at line 289 of file par12_hispi_psp4l.v.

|

Parameter |

Definition at line 290 of file par12_hispi_psp4l.v.

|

Parameter |

Definition at line 291 of file par12_hispi_psp4l.v.

|

Parameter |

Definition at line 292 of file par12_hispi_psp4l.v.

|

Parameter |

Definition at line 293 of file par12_hispi_psp4l.v.

|

Parameter |

Definition at line 294 of file par12_hispi_psp4l.v.

|

Input |

Definition at line 296 of file par12_hispi_psp4l.v.

|

Input |

Definition at line 297 of file par12_hispi_psp4l.v.

|

Input |

Definition at line 298 of file par12_hispi_psp4l.v.

|

Input |

Definition at line 299 of file par12_hispi_psp4l.v.

|

Input |

Definition at line 300 of file par12_hispi_psp4l.v.

|

Output |

Definition at line 301 of file par12_hispi_psp4l.v.

|

Output |

Definition at line 302 of file par12_hispi_psp4l.v.

|

Output |

Definition at line 303 of file par12_hispi_psp4l.v.

|

Signal |

Definition at line 305 of file par12_hispi_psp4l.v.

|

Signal |

Definition at line 306 of file par12_hispi_psp4l.v.

|

Signal |

Definition at line 307 of file par12_hispi_psp4l.v.

|

Signal |

Definition at line 308 of file par12_hispi_psp4l.v.

|

Signal |

Definition at line 309 of file par12_hispi_psp4l.v.

|

Signal |

Definition at line 310 of file par12_hispi_psp4l.v.

|

Signal |

Definition at line 311 of file par12_hispi_psp4l.v.

|

Signal |

Definition at line 312 of file par12_hispi_psp4l.v.

|

Signal |

Definition at line 313 of file par12_hispi_psp4l.v.

|

Signal |

Definition at line 314 of file par12_hispi_psp4l.v.

|

Signal |

Definition at line 315 of file par12_hispi_psp4l.v.

|

Signal |

Definition at line 317 of file par12_hispi_psp4l.v.

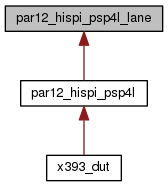

The documentation for this Module was generated from the following files:

- simulation_modules/par12_hispi_psp4l.v