Public Attributes |

Inputs | |

| CPLLREFCLKSEL | wire [ 2 : 0 ] |

| GTREFCLK0 | wire |

| GTREFCLK1 | wire |

| GTNORTHREFCLK0 | wire |

| GTNORTHREFCLK1 | wire |

| GTSOUTHREFCLK0 | wire |

| GTSOUTHREFCLK1 | wire |

| GTGREFCLK | wire |

| QPLLCLK | wire |

| QPLLREFCLK | wire |

| RXSYSCLKSEL | wire [ 1 : 0 ] |

| TXSYSCLKSEL | wire [ 1 : 0 ] |

| TXOUTCLKSEL | wire [ 2 : 0 ] |

| RXOUTCLKSEL | wire [ 2 : 0 ] |

| TXDLYBYPASS | wire |

| RXDLYBYPASS | wire |

| CPLLLOCKDETCLK | wire |

| CPLLLOCKEN | wire |

| CPLLPD | wire |

| CPLLRESET | wire |

| TXRATE | wire [ 2 : 0 ] |

| RXRATE | wire [ 2 : 0 ] |

| GTRSVD | [ 15 : 0 ] |

| PCSRSVDIN | [ 15 : 0 ] |

| PCSRSVDIN2 | [ 4 : 0 ] |

| PMARSVDIN | [ 4 : 0 ] |

| PMARSVDIN2 | [ 4 : 0 ] |

| TSTIN | [ 19 : 0 ] |

Outputs | |

| GTREFCLKMONITOR | wire |

| CPLLFBCLKLOST | wire |

| CPLLLOCK | wire |

| CPLLREFCLKLOST | wire |

| TXOUTCLKPMA | wire |

| TXOUTCLKPCS | wire |

| TXOUTCLK | wire |

| TXOUTCLKFABRIC | wire |

| tx_serial_clk | wire |

| tx_piso_clk | wire |

| RXOUTCLKPMA | wire |

| RXOUTCLKPCS | wire |

| RXOUTCLK | wire |

| RXOUTCLKFABRIC | wire |

| rx_serial_clk | wire |

| rx_sipo_clk | wire |

| TSTOUT | [ 9 : 0 ] |

Parameters | |

| CPLL_CFG | [ 23 : 0 ] 29 'h00BC07DC |

| CPLL_FBDIV | integer 4 |

| CPLL_FBDIV_45 | integer 5 |

| CPLL_INIT_CFG | [ 23 : 0 ] 24 'h00001E |

| CPLL_LOCK_CFG | [ 15 : 0 ] 16 'h01E8 |

| CPLL_REFCLK_DIV | integer 1 |

| SATA_CPLL_CFG | "VCO_3000MHZ" |

| PMA_RSV3 | [ 1 : 0 ] 1 |

| TXOUT_DIV | 2 |

| RXOUT_DIV | 2 |

| TX_INT_DATAWIDTH | 0 |

| TX_DATA_WIDTH | 20 |

| RX_INT_DATAWIDTH | 0 |

| RX_DATA_WIDTH | 20 |

| tx_pma_divider1 | TX_INT_DATAWIDTH == 1 ? 4 : 2 |

| tx_pcs_divider1 | tx_pma_divider1 |

| tx_pma_divider2 | TX_DATA_WIDTH == 20 | TX_DATA_WIDTH == 40 | TX_DATA_WIDTH == 80 ? 5 : 4 |

| tx_pcs_divider2 | tx_pma_divider2 |

| rx_pma_divider1 | RX_INT_DATAWIDTH == 1 ? 4 : 2 |

| rx_pma_divider2 | RX_DATA_WIDTH == 20 | RX_DATA_WIDTH == 40 | RX_DATA_WIDTH == 80 ? 5 : 4 |

Defines | |

| RESYNC_FIFO_NOSYNT_V | |

Signals | |

| wire | clk_mux_out |

| wire | cpll_clk_out |

| wire | tx_phy_clk |

| wire | rx_phy_clk |

| wire | TXPLLREFCLK_DIV1 |

| wire | TXPLLREFCLK_DIV2 |

| wire | RXPLLREFCLK_DIV1 |

| wire | RXPLLREFCLK_DIV2 |

| wire[ 31 : 0 ] | tx_serial_divider |

| wire[ 31 : 0 ] | rx_serial_divider |

| wire | tx_pma_div1_clk |

| wire | rx_pma_div1_clk |

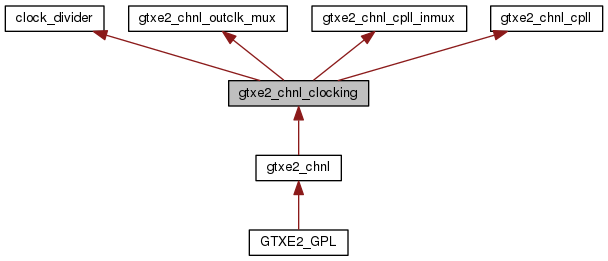

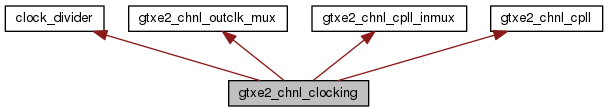

Detailed Description

Definition at line 261 of file GTXE2_GPL.v.

Member Data Documentation

|

Input |

Definition at line 263 of file GTXE2_GPL.v.

|

Input |

Definition at line 264 of file GTXE2_GPL.v.

|

Input |

Definition at line 265 of file GTXE2_GPL.v.

|

Input |

Definition at line 266 of file GTXE2_GPL.v.

|

Input |

Definition at line 267 of file GTXE2_GPL.v.

|

Input |

Definition at line 268 of file GTXE2_GPL.v.

|

Input |

Definition at line 269 of file GTXE2_GPL.v.

|

Input |

Definition at line 270 of file GTXE2_GPL.v.

|

Input |

Definition at line 271 of file GTXE2_GPL.v.

|

Input |

Definition at line 272 of file GTXE2_GPL.v.

|

Input |

Definition at line 273 of file GTXE2_GPL.v.

|

Input |

Definition at line 274 of file GTXE2_GPL.v.

|

Input |

Definition at line 275 of file GTXE2_GPL.v.

|

Input |

Definition at line 276 of file GTXE2_GPL.v.

|

Input |

Definition at line 277 of file GTXE2_GPL.v.

|

Input |

Definition at line 278 of file GTXE2_GPL.v.

|

Output |

Definition at line 279 of file GTXE2_GPL.v.

|

Input |

Definition at line 281 of file GTXE2_GPL.v.

|

Input |

Definition at line 282 of file GTXE2_GPL.v.

|

Input |

Definition at line 283 of file GTXE2_GPL.v.

|

Input |

Definition at line 284 of file GTXE2_GPL.v.

|

Output |

Definition at line 285 of file GTXE2_GPL.v.

|

Output |

Definition at line 286 of file GTXE2_GPL.v.

|

Output |

Definition at line 287 of file GTXE2_GPL.v.

|

Input |

Definition at line 289 of file GTXE2_GPL.v.

|

Input |

Definition at line 290 of file GTXE2_GPL.v.

|

Output |

Definition at line 293 of file GTXE2_GPL.v.

|

Output |

Definition at line 294 of file GTXE2_GPL.v.

|

Output |

Definition at line 295 of file GTXE2_GPL.v.

|

Output |

Definition at line 296 of file GTXE2_GPL.v.

|

Output |

Definition at line 297 of file GTXE2_GPL.v.

|

Output |

Definition at line 298 of file GTXE2_GPL.v.

|

Output |

Definition at line 300 of file GTXE2_GPL.v.

|

Output |

Definition at line 301 of file GTXE2_GPL.v.

|

Output |

Definition at line 302 of file GTXE2_GPL.v.

|

Output |

Definition at line 303 of file GTXE2_GPL.v.

|

Output |

Definition at line 304 of file GTXE2_GPL.v.

|

Output |

Definition at line 305 of file GTXE2_GPL.v.

|

Output |

Definition at line 308 of file GTXE2_GPL.v.

|

Input |

Definition at line 309 of file GTXE2_GPL.v.

|

Input |

Definition at line 310 of file GTXE2_GPL.v.

|

Input |

Definition at line 311 of file GTXE2_GPL.v.

|

Input |

Definition at line 312 of file GTXE2_GPL.v.

|

Input |

Definition at line 313 of file GTXE2_GPL.v.

|

Input |

Definition at line 314 of file GTXE2_GPL.v.

|

Parameter |

Definition at line 317 of file GTXE2_GPL.v.

|

Parameter |

Definition at line 318 of file GTXE2_GPL.v.

|

Parameter |

Definition at line 319 of file GTXE2_GPL.v.

|

Parameter |

Definition at line 320 of file GTXE2_GPL.v.

|

Parameter |

Definition at line 321 of file GTXE2_GPL.v.

|

Parameter |

Definition at line 322 of file GTXE2_GPL.v.

|

Parameter |

Definition at line 323 of file GTXE2_GPL.v.

|

Parameter |

Definition at line 324 of file GTXE2_GPL.v.

|

Parameter |

Definition at line 326 of file GTXE2_GPL.v.

|

Parameter |

Definition at line 328 of file GTXE2_GPL.v.

|

Parameter |

Definition at line 331 of file GTXE2_GPL.v.

|

Parameter |

Definition at line 332 of file GTXE2_GPL.v.

|

Parameter |

Definition at line 333 of file GTXE2_GPL.v.

|

Parameter |

Definition at line 334 of file GTXE2_GPL.v.

|

Parameter |

Definition at line 347 of file GTXE2_GPL.v.

|

Parameter |

Definition at line 348 of file GTXE2_GPL.v.

|

Parameter |

Definition at line 349 of file GTXE2_GPL.v.

|

Parameter |

Definition at line 350 of file GTXE2_GPL.v.

|

Parameter |

Definition at line 351 of file GTXE2_GPL.v.

|

Parameter |

Definition at line 352 of file GTXE2_GPL.v.

|

Signal |

Definition at line 354 of file GTXE2_GPL.v.

|

Signal |

Definition at line 355 of file GTXE2_GPL.v.

|

Signal |

Definition at line 356 of file GTXE2_GPL.v.

|

Signal |

Definition at line 357 of file GTXE2_GPL.v.

|

Signal |

Definition at line 358 of file GTXE2_GPL.v.

|

Signal |

Definition at line 359 of file GTXE2_GPL.v.

|

Signal |

Definition at line 360 of file GTXE2_GPL.v.

|

Signal |

Definition at line 361 of file GTXE2_GPL.v.

|

Signal |

Definition at line 373 of file GTXE2_GPL.v.

|

Signal |

Definition at line 374 of file GTXE2_GPL.v.

|

Signal |

Definition at line 407 of file GTXE2_GPL.v.

|

Signal |

Definition at line 429 of file GTXE2_GPL.v.

|

Module Instance |

Definition at line 385 of file GTXE2_GPL.v.

|

Module Instance |

Definition at line 395 of file GTXE2_GPL.v.

|

Module Instance |

Definition at line 410 of file GTXE2_GPL.v.

|

Module Instance |

Definition at line 419 of file GTXE2_GPL.v.

|

Module Instance |

Definition at line 431 of file GTXE2_GPL.v.

|

Module Instance |

Definition at line 440 of file GTXE2_GPL.v.

|

Module Instance |

Definition at line 450 of file GTXE2_GPL.v.

|

Module Instance |

Definition at line 458 of file GTXE2_GPL.v.

|

Module Instance |

Definition at line 502 of file GTXE2_GPL.v.

|

Module Instance |

Definition at line 488 of file GTXE2_GPL.v.

|

Module Instance |

Definition at line 467 of file GTXE2_GPL.v.

|

Module Instance |

Definition at line 477 of file GTXE2_GPL.v.

|

Define |

Definition at line 535 of file GTXE2_GPL.v.

The documentation for this Module was generated from the following files:

- x393_sata/wrapper/GTXE2_GPL.v