gtxe2_chnl_outclk_mux Module Reference

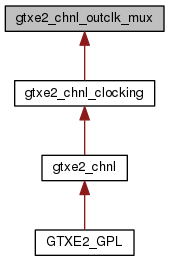

Inheritance diagram for gtxe2_chnl_outclk_mux:

Public Attributes |

Inputs | |

| TXPLLREFCLK_DIV1 | wire |

| TXPLLREFCLK_DIV2 | wire |

| TXOUTCLKPMA | wire |

| TXOUTCLKPCS | wire |

| TXOUTCLKSEL | wire [ 2 : 0 ] |

| TXDLYBYPASS | wire |

Outputs | |

| TXOUTCLK | wire |

Defines | |

| GTXE2_CHNL_CPLL_LOCK_TIME | 60 |

Detailed Description

Definition at line 73 of file GTXE2_GPL.v.

Member Data Documentation

|

Input |

Definition at line 74 of file GTXE2_GPL.v.

|

Input |

Definition at line 75 of file GTXE2_GPL.v.

|

Input |

Definition at line 76 of file GTXE2_GPL.v.

|

Input |

Definition at line 77 of file GTXE2_GPL.v.

|

Input |

Definition at line 78 of file GTXE2_GPL.v.

|

Input |

Definition at line 79 of file GTXE2_GPL.v.

|

Output |

Definition at line 80 of file GTXE2_GPL.v.

|

Define |

Definition at line 91 of file GTXE2_GPL.v.

The documentation for this Module was generated from the following files:

- x393_sata/wrapper/GTXE2_GPL.v