Static Public Member Functions |

Always Constructs | |

| ALWAYS_574 | ( mclk ) |

| ALWAYS_575 | ( hclk ) |

| ALWAYS_576 | ( hclk ) |

Public Attributes |

Inputs | |

| mrst | |

| hrst | |

| mclk | |

| hclk | |

| ctba | [ 31 : 4 ] |

| ctba_ld | |

| prdtl | [ 15 : 0 ] |

| dev_wr | |

| cmd_start | |

| prd_start | |

| cmd_abort | |

| axi_wr_cache_mode | [ 3 : 0 ] |

| axi_rd_cache_mode | [ 3 : 0 ] |

| set_axi_wr_cache_mode | |

| set_axi_rd_cache_mode | |

| ct_addr | [ 4 : 0 ] |

| ct_re | [ 1 : 0 ] |

| prd_irq_clear | |

| sys_re | |

| sys_in | [ 31 : 0 ] |

| sys_we | |

| afi_awready | |

| afi_wready | |

| afi_bvalid | |

| afi_bid | [ 5 : 0 ] |

| afi_bresp | [ 1 : 0 ] |

| afi_wcount | [ 7 : 0 ] |

| afi_wacount | [ 5 : 0 ] |

| afi_arready | |

| afi_rdata | [ 63 : 0 ] |

| afi_rvalid | |

| afi_rid | [ 5 : 0 ] |

| afi_rlast | |

| afi_rresp | [ 1 : 0 ] |

| afi_rcount | [ 7 : 0 ] |

| afi_racount | [ 2 : 0 ] |

Outputs | |

| ct_busy | reg |

| ct_data | reg [ 31 : 0 ] |

| prd_done | |

| prd_irq_pend | reg |

| cmd_busy | reg |

| cmd_done | |

| abort_busy | |

| abort_done | |

| axi_mismatch | |

| sys_out | [ 31 : 0 ] |

| sys_dav | |

| last_h2d_data | |

| sys_nfull | |

| extra_din | |

| afi_awaddr | [ 31 : 0 ] |

| afi_awvalid | |

| afi_awid | [ 5 : 0 ] |

| afi_awlock | [ 1 : 0 ] |

| afi_awcache | reg [ 3 : 0 ] |

| afi_awprot | [ 2 : 0 ] |

| afi_awlen | [ 3 : 0 ] |

| afi_awsize | [ 1 : 0 ] |

| afi_awburst | [ 1 : 0 ] |

| afi_awqos | [ 3 : 0 ] |

| afi_wdata | [ 63 : 0 ] |

| afi_wvalid | |

| afi_wid | [ 5 : 0 ] |

| afi_wlast | |

| afi_wstrb | [ 7 : 0 ] |

| afi_bready | |

| afi_wrissuecap1en | |

| afi_araddr | [ 31 : 0 ] |

| afi_arvalid | |

| afi_arid | [ 5 : 0 ] |

| afi_arlock | [ 1 : 0 ] |

| afi_arcache | reg [ 3 : 0 ] |

| afi_arprot | [ 2 : 0 ] |

| afi_arlen | [ 3 : 0 ] |

| afi_arsize | [ 1 : 0 ] |

| afi_arburst | [ 1 : 0 ] |

| afi_arqos | [ 3 : 0 ] |

| afi_rready | |

| afi_rdissuecap1en | |

| debug_out | [ 31 : 0 ] |

| debug_out1 | [ 31 : 0 ] |

| debug_dma_h2d | [ 31 : 0 ] |

Parameters | |

| SAFE_RD_BITS | 3 |

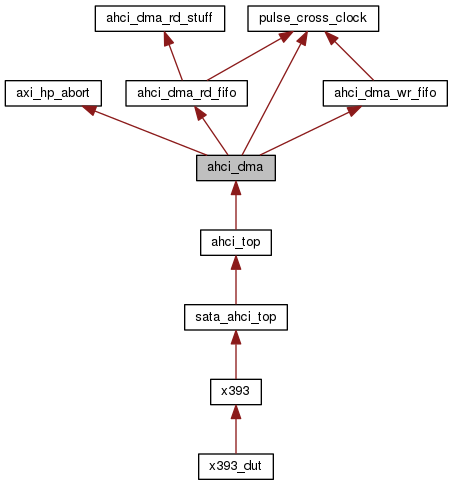

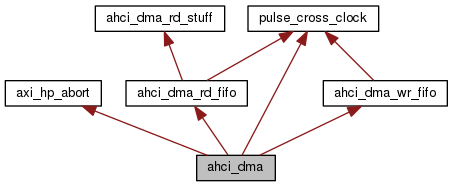

Detailed Description

Definition at line 41 of file ahci_dma.v.

Member Function Documentation

|

Always Construct |

Definition at line 339 of file ahci_dma.v.

|

Always Construct |

Definition at line 392 of file ahci_dma.v.

|

Always Construct |

Definition at line 723 of file ahci_dma.v.

Member Data Documentation

|

Input |

Definition at line 43 of file ahci_dma.v.

|

Input |

Definition at line 44 of file ahci_dma.v.

|

Input |

Definition at line 46 of file ahci_dma.v.

|

Input |

Definition at line 47 of file ahci_dma.v.

|

Input |

Definition at line 51 of file ahci_dma.v.

|

Input |

Definition at line 52 of file ahci_dma.v.

|

Input |

Definition at line 53 of file ahci_dma.v.

|

Input |

Definition at line 54 of file ahci_dma.v.

|

Input |

Definition at line 55 of file ahci_dma.v.

|

Input |

Definition at line 56 of file ahci_dma.v.

|

Input |

Definition at line 57 of file ahci_dma.v.

|

Input |

Definition at line 61 of file ahci_dma.v.

|

Input |

Definition at line 62 of file ahci_dma.v.

|

Input |

Definition at line 63 of file ahci_dma.v.

|

Input |

Definition at line 64 of file ahci_dma.v.

|

Output |

Definition at line 68 of file ahci_dma.v.

|

Input |

Definition at line 70 of file ahci_dma.v.

|

Input |

Definition at line 71 of file ahci_dma.v.

|

Output |

Definition at line 72 of file ahci_dma.v.

|

Output |

Definition at line 76 of file ahci_dma.v.

|

Input |

Definition at line 77 of file ahci_dma.v.

|

Output |

Definition at line 78 of file ahci_dma.v.

|

Output |

Definition at line 79 of file ahci_dma.v.

|

Output |

Definition at line 80 of file ahci_dma.v.

|

Output |

Definition at line 81 of file ahci_dma.v.

|

Output |

Definition at line 82 of file ahci_dma.v.

|

Output |

Definition at line 83 of file ahci_dma.v.

|

Output |

Definition at line 86 of file ahci_dma.v.

|

Output |

Definition at line 87 of file ahci_dma.v.

|

Input |

Definition at line 89 of file ahci_dma.v.

|

Output |

Definition at line 90 of file ahci_dma.v.

|

Input |

Definition at line 93 of file ahci_dma.v.

|

Output |

Definition at line 94 of file ahci_dma.v.

|

Input |

Definition at line 95 of file ahci_dma.v.

|

Output |

Definition at line 97 of file ahci_dma.v.

|

Output |

Definition at line 101 of file ahci_dma.v.

|

Output |

Definition at line 102 of file ahci_dma.v.

|

Input |

Definition at line 103 of file ahci_dma.v.

|

Output |

Definition at line 104 of file ahci_dma.v.

|

Output |

Definition at line 105 of file ahci_dma.v.

|

Output |

Definition at line 106 of file ahci_dma.v.

|

Output |

Definition at line 107 of file ahci_dma.v.

|

Output |

Definition at line 108 of file ahci_dma.v.

|

Output |

Definition at line 109 of file ahci_dma.v.

|

Output |

Definition at line 110 of file ahci_dma.v.

|

Output |

Definition at line 111 of file ahci_dma.v.

|

Output |

Definition at line 113 of file ahci_dma.v.

|

Output |

Definition at line 114 of file ahci_dma.v.

|

Input |

Definition at line 115 of file ahci_dma.v.

|

Output |

Definition at line 116 of file ahci_dma.v.

|

Output |

Definition at line 117 of file ahci_dma.v.

|

Output |

Definition at line 118 of file ahci_dma.v.

|

Input |

Definition at line 120 of file ahci_dma.v.

|

Output |

Definition at line 121 of file ahci_dma.v.

|

Input |

Definition at line 122 of file ahci_dma.v.

|

Input |

Definition at line 123 of file ahci_dma.v.

|

Input |

Definition at line 125 of file ahci_dma.v.

|

Input |

Definition at line 126 of file ahci_dma.v.

|

Output |

Definition at line 127 of file ahci_dma.v.

|

Output |

Definition at line 130 of file ahci_dma.v.

|

Output |

Definition at line 131 of file ahci_dma.v.

|

Input |

Definition at line 132 of file ahci_dma.v.

|

Output |

Definition at line 133 of file ahci_dma.v.

|

Output |

Definition at line 134 of file ahci_dma.v.

|

Output |

Definition at line 135 of file ahci_dma.v.

|

Output |

Definition at line 136 of file ahci_dma.v.

|

Output |

Definition at line 137 of file ahci_dma.v.

|

Output |

Definition at line 138 of file ahci_dma.v.

|

Output |

Definition at line 139 of file ahci_dma.v.

|

Output |

Definition at line 140 of file ahci_dma.v.

|

Input |

Definition at line 142 of file ahci_dma.v.

|

Input |

Definition at line 143 of file ahci_dma.v.

|

Output |

Definition at line 144 of file ahci_dma.v.

|

Input |

Definition at line 145 of file ahci_dma.v.

|

Input |

Definition at line 146 of file ahci_dma.v.

|

Input |

Definition at line 147 of file ahci_dma.v.

|

Input |

Definition at line 149 of file ahci_dma.v.

|

Input |

Definition at line 150 of file ahci_dma.v.

|

Output |

Definition at line 151 of file ahci_dma.v.

|

Output |

Definition at line 153 of file ahci_dma.v.

|

Output |

Definition at line 154 of file ahci_dma.v.

|

Output |

Definition at line 156 of file ahci_dma.v.

|

Parameter |

Definition at line 163 of file ahci_dma.v.

|

Signal |

Definition at line 165 of file ahci_dma.v.

|

Signal |

Definition at line 166 of file ahci_dma.v.

|

Signal |

Definition at line 168 of file ahci_dma.v.

|

Signal |

Definition at line 169 of file ahci_dma.v.

|

Signal |

Definition at line 170 of file ahci_dma.v.

|

Signal |

Definition at line 171 of file ahci_dma.v.

|

Signal |

Definition at line 172 of file ahci_dma.v.

|

Signal |

Definition at line 173 of file ahci_dma.v.

|

Signal |

Definition at line 174 of file ahci_dma.v.

|

Signal |

Definition at line 175 of file ahci_dma.v.

|

Signal |

Definition at line 176 of file ahci_dma.v.

|

Signal |

Definition at line 178 of file ahci_dma.v.

|

Signal |

Definition at line 179 of file ahci_dma.v.

|

Signal |

Definition at line 180 of file ahci_dma.v.

|

Signal |

Definition at line 181 of file ahci_dma.v.

|

Signal |

Definition at line 182 of file ahci_dma.v.

|

Signal |

Definition at line 184 of file ahci_dma.v.

|

Signal |

Definition at line 185 of file ahci_dma.v.

|

Signal |

Definition at line 186 of file ahci_dma.v.

|

Signal |

Definition at line 187 of file ahci_dma.v.

|

Signal |

Definition at line 189 of file ahci_dma.v.

|

Signal |

Definition at line 190 of file ahci_dma.v.

|

Signal |

Definition at line 191 of file ahci_dma.v.

|

Signal |

Definition at line 192 of file ahci_dma.v.

|

Signal |

Definition at line 193 of file ahci_dma.v.

|

Signal |

Definition at line 195 of file ahci_dma.v.

|

Signal |

Definition at line 196 of file ahci_dma.v.

|

Signal |

Definition at line 197 of file ahci_dma.v.

|

Signal |

Definition at line 198 of file ahci_dma.v.

|

Signal |

Definition at line 199 of file ahci_dma.v.

|

Signal |

Definition at line 200 of file ahci_dma.v.

|

Signal |

Definition at line 201 of file ahci_dma.v.

|

Signal |

Definition at line 203 of file ahci_dma.v.

|

Signal |

Definition at line 204 of file ahci_dma.v.

|

Signal |

Definition at line 205 of file ahci_dma.v.

|

Signal |

Definition at line 207 of file ahci_dma.v.

|

Signal |

Definition at line 209 of file ahci_dma.v.

|

Signal |

Definition at line 210 of file ahci_dma.v.

|

Signal |

Definition at line 212 of file ahci_dma.v.

|

Signal |

Definition at line 213 of file ahci_dma.v.

|

Signal |

Definition at line 214 of file ahci_dma.v.

|

Signal |

Definition at line 216 of file ahci_dma.v.

|

Signal |

Definition at line 217 of file ahci_dma.v.

|

Signal |

Definition at line 218 of file ahci_dma.v.

|

Signal |

Definition at line 219 of file ahci_dma.v.

|

Signal |

Definition at line 220 of file ahci_dma.v.

|

Signal |

Definition at line 222 of file ahci_dma.v.

|

Signal |

Definition at line 223 of file ahci_dma.v.

|

Signal |

Definition at line 224 of file ahci_dma.v.

|

Signal |

Definition at line 225 of file ahci_dma.v.

|

Signal |

Definition at line 226 of file ahci_dma.v.

|

Signal |

Definition at line 227 of file ahci_dma.v.

|

Signal |

Definition at line 228 of file ahci_dma.v.

|

Signal |

Definition at line 229 of file ahci_dma.v.

|

Signal |

Definition at line 231 of file ahci_dma.v.

|

Signal |

Definition at line 234 of file ahci_dma.v.

|

Signal |

Definition at line 236 of file ahci_dma.v.

|

Signal |

Definition at line 238 of file ahci_dma.v.

|

Signal |

Definition at line 239 of file ahci_dma.v.

|

Signal |

Definition at line 248 of file ahci_dma.v.

|

Signal |

Definition at line 249 of file ahci_dma.v.

|

Signal |

Definition at line 251 of file ahci_dma.v.

|

Signal |

Definition at line 252 of file ahci_dma.v.

|

Signal |

Definition at line 254 of file ahci_dma.v.

|

Signal |

Definition at line 255 of file ahci_dma.v.

|

Signal |

Definition at line 257 of file ahci_dma.v.

|

Signal |

Definition at line 258 of file ahci_dma.v.

|

Signal |

Definition at line 259 of file ahci_dma.v.

|

Signal |

Definition at line 260 of file ahci_dma.v.

|

Signal |

Definition at line 261 of file ahci_dma.v.

|

Signal |

Definition at line 263 of file ahci_dma.v.

|

Signal |

Definition at line 264 of file ahci_dma.v.

|

Signal |

Definition at line 265 of file ahci_dma.v.

|

Signal |

Definition at line 267 of file ahci_dma.v.

|

Signal |

Definition at line 268 of file ahci_dma.v.

|

Signal |

Definition at line 271 of file ahci_dma.v.

|

Signal |

Definition at line 272 of file ahci_dma.v.

|

Signal |

Definition at line 273 of file ahci_dma.v.

|

Signal |

Definition at line 274 of file ahci_dma.v.

|

Signal |

Definition at line 275 of file ahci_dma.v.

|

Signal |

Definition at line 276 of file ahci_dma.v.

|

Signal |

Definition at line 277 of file ahci_dma.v.

|

Signal |

Definition at line 278 of file ahci_dma.v.

|

Signal |

Definition at line 279 of file ahci_dma.v.

|

Signal |

Definition at line 280 of file ahci_dma.v.

|

Signal |

Definition at line 281 of file ahci_dma.v.

|

Signal |

Definition at line 283 of file ahci_dma.v.

|

Signal |

Definition at line 284 of file ahci_dma.v.

|

Signal |

Definition at line 285 of file ahci_dma.v.

|

Signal |

Definition at line 286 of file ahci_dma.v.

|

Signal |

Definition at line 386 of file ahci_dma.v.

|

Signal |

Definition at line 387 of file ahci_dma.v.

|

Signal |

Definition at line 388 of file ahci_dma.v.

|

Signal |

Definition at line 390 of file ahci_dma.v.

|

Signal |

Definition at line 715 of file ahci_dma.v.

|

Signal |

Definition at line 716 of file ahci_dma.v.

|

Signal |

Definition at line 717 of file ahci_dma.v.

|

Signal |

Definition at line 718 of file ahci_dma.v.

|

Signal |

Definition at line 719 of file ahci_dma.v.

|

Signal |

Definition at line 720 of file ahci_dma.v.

|

Module Instance |

Definition at line 584 of file ahci_dma.v.

|

Module Instance |

Definition at line 610 of file ahci_dma.v.

|

Module Instance |

Definition at line 553 of file ahci_dma.v.

|

Module Instance |

Definition at line 636 of file ahci_dma.v.

|

Module Instance |

Definition at line 646 of file ahci_dma.v.

|

Module Instance |

Definition at line 656 of file ahci_dma.v.

|

Module Instance |

Definition at line 670 of file ahci_dma.v.

|

Module Instance |

Definition at line 681 of file ahci_dma.v.

|

Module Instance |

Definition at line 692 of file ahci_dma.v.

|

Module Instance |

Definition at line 703 of file ahci_dma.v.

The documentation for this Module was generated from the following files:

- x393_sata/ahci/ahci_dma.v