Static Public Member Functions |

Always Constructs | |

| ALWAYS_580 | ( hclk ) |

| ALWAYS_581 | ( mclk ) |

| ALWAYS_582 | ( ** ) |

Public Attributes |

Inputs | |

| mrst | |

| hrst | |

| mclk | |

| hclk | |

| wcnt | [WCNT_BITS - 1 : 0 ] |

| woffs | [ 1 : 0 ] |

| init | |

| start | |

| dout_av_many | |

| last_prd | |

| din | [ 31 : 0 ] |

| din_avail | |

Outputs | |

| dout | reg [ 63 : 0 ] |

| dout_we | |

| dout_wstb | reg [ 3 : 0 ] |

| done | reg |

| busy | |

| fifo_nempty_mclk | reg |

| din_rdy | |

Parameters | |

| WCNT_BITS | 21 |

| ADDRESS_BITS | 3 |

| ADDRESS_NUM | (1<<ADDRESS_BITS |

Signals | |

| reg[ 31 : 0 ] | fifo0_ram [ 0 :ADDRESS_NUM - 1 ] |

| reg[ 31 : 0 ] | fifo1_ram [ 0 :ADDRESS_NUM - 1 ] |

| wire | init_mclk |

| wire | init_confirm |

| reg | en_fifo_rd |

| reg | en_fifo_wr |

| wire | flush_hclk |

| wire | flush_mclk |

| reg[ADDRESS_BITS : 0 ] | raddr |

| reg[ADDRESS_BITS + 1 : 0 ] | waddr |

| reg[ 63 : 16 ] | fifo_do_prev |

| reg[1<<ADDRESS_BITS- 1 : 0 ] | fifo_full |

| reg[1<<ADDRESS_BITS- 1 : 0 ] | fifo_nempty |

| wire | fifo_wr |

| wire[1<<ADDRESS_BITS- 1 : 0 ] | fifo_full2 |

| reg | hrst_mclk |

| reg | fifo_dav |

| reg | fifo_dav2 |

| reg | fifo_half_mclk |

| wire[ 63 : 0 ] | fifo_do |

| wire | dout_we_w |

| reg[ 1 : 0 ] | dout_we_r |

| reg[ 1 : 0 ] | wp |

| reg[ 1 : 0 ] | fp |

| reg[ 1 : 0 ] | wl |

| reg[ 1 : 0 ] | mx0 |

| reg[ 2 : 0 ] | mx1 |

| reg[ 2 : 0 ] | mx2 |

| reg[ 2 : 0 ] | mx3 |

| reg[ 3 : 0 ] | pm |

| wire | fifo_rd |

| reg | fifo_rd_r |

| reg[ 1 : 0 ] | nfp |

| reg[ 2 : 0 ] | swl |

| reg | need_fifo |

| reg | busy_r |

| reg | is_last_prd |

| reg[WCNT_BITS - 1 : 0 ] | wcntr |

| wire[WCNT_BITS - 1 : 0 ] | next_wcntr |

| reg | flushing |

| wire | last_qword |

| wire | done_w |

| wire | axi_ready |

| wire | fifo_out_ready |

Module Instances | |

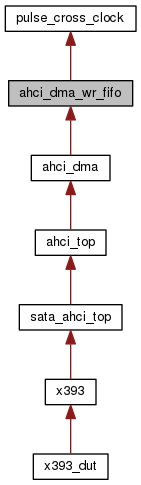

| pulse_cross_clock::init_mclk_i | Module pulse_cross_clock |

| pulse_cross_clock::flush_mclk_i | Module pulse_cross_clock |

| pulse_cross_clock::init_confirm_i | Module pulse_cross_clock |

Detailed Description

Definition at line 43 of file ahci_dma_wr_fifo.v.

Member Function Documentation

|

Always Construct |

Definition at line 145 of file ahci_dma_wr_fifo.v.

|

Always Construct |

Definition at line 262 of file ahci_dma_wr_fifo.v.

|

Always Construct |

Definition at line 344 of file ahci_dma_wr_fifo.v.

Member Data Documentation

|

Parameter |

Definition at line 44 of file ahci_dma_wr_fifo.v.

|

Parameter |

Definition at line 45 of file ahci_dma_wr_fifo.v.

|

Input |

Definition at line 47 of file ahci_dma_wr_fifo.v.

|

Input |

Definition at line 48 of file ahci_dma_wr_fifo.v.

|

Input |

Definition at line 49 of file ahci_dma_wr_fifo.v.

|

Input |

Definition at line 50 of file ahci_dma_wr_fifo.v.

Definition at line 52 of file ahci_dma_wr_fifo.v.

|

Input |

Definition at line 53 of file ahci_dma_wr_fifo.v.

|

Input |

Definition at line 54 of file ahci_dma_wr_fifo.v.

|

Input |

Definition at line 55 of file ahci_dma_wr_fifo.v.

|

Output |

Definition at line 56 of file ahci_dma_wr_fifo.v.

|

Input |

Definition at line 58 of file ahci_dma_wr_fifo.v.

|

Input |

Definition at line 59 of file ahci_dma_wr_fifo.v.

|

Output |

Definition at line 61 of file ahci_dma_wr_fifo.v.

|

Output |

Definition at line 62 of file ahci_dma_wr_fifo.v.

|

Output |

Definition at line 63 of file ahci_dma_wr_fifo.v.

|

Output |

Definition at line 65 of file ahci_dma_wr_fifo.v.

|

Output |

Definition at line 67 of file ahci_dma_wr_fifo.v.

|

Input |

Definition at line 69 of file ahci_dma_wr_fifo.v.

|

Output |

Definition at line 70 of file ahci_dma_wr_fifo.v.

|

Input |

Definition at line 71 of file ahci_dma_wr_fifo.v.

|

Parameter |

Definition at line 73 of file ahci_dma_wr_fifo.v.

|

Signal |

Definition at line 74 of file ahci_dma_wr_fifo.v.

|

Signal |

Definition at line 75 of file ahci_dma_wr_fifo.v.

|

Signal |

Definition at line 76 of file ahci_dma_wr_fifo.v.

|

Signal |

Definition at line 77 of file ahci_dma_wr_fifo.v.

|

Signal |

Definition at line 78 of file ahci_dma_wr_fifo.v.

|

Signal |

Definition at line 79 of file ahci_dma_wr_fifo.v.

|

Signal |

Definition at line 80 of file ahci_dma_wr_fifo.v.

|

Signal |

Definition at line 81 of file ahci_dma_wr_fifo.v.

|

Signal |

Definition at line 83 of file ahci_dma_wr_fifo.v.

|

Signal |

Definition at line 84 of file ahci_dma_wr_fifo.v.

|

Signal |

Definition at line 85 of file ahci_dma_wr_fifo.v.

|

Signal |

Definition at line 86 of file ahci_dma_wr_fifo.v.

|

Signal |

Definition at line 87 of file ahci_dma_wr_fifo.v.

|

Signal |

Definition at line 88 of file ahci_dma_wr_fifo.v.

|

Signal |

Definition at line 90 of file ahci_dma_wr_fifo.v.

|

Signal |

Definition at line 91 of file ahci_dma_wr_fifo.v.

|

Signal |

Definition at line 92 of file ahci_dma_wr_fifo.v.

|

Signal |

Definition at line 93 of file ahci_dma_wr_fifo.v.

|

Signal |

Definition at line 94 of file ahci_dma_wr_fifo.v.

|

Signal |

Definition at line 96 of file ahci_dma_wr_fifo.v.

|

Signal |

Definition at line 97 of file ahci_dma_wr_fifo.v.

|

Signal |

Definition at line 98 of file ahci_dma_wr_fifo.v.

|

Signal |

Definition at line 100 of file ahci_dma_wr_fifo.v.

|

Signal |

Definition at line 101 of file ahci_dma_wr_fifo.v.

|

Signal |

Definition at line 102 of file ahci_dma_wr_fifo.v.

|

Signal |

Definition at line 104 of file ahci_dma_wr_fifo.v.

|

Signal |

Definition at line 105 of file ahci_dma_wr_fifo.v.

|

Signal |

Definition at line 106 of file ahci_dma_wr_fifo.v.

|

Signal |

Definition at line 107 of file ahci_dma_wr_fifo.v.

|

Signal |

Definition at line 108 of file ahci_dma_wr_fifo.v.

|

Signal |

Definition at line 109 of file ahci_dma_wr_fifo.v.

|

Signal |

Definition at line 110 of file ahci_dma_wr_fifo.v.

|

Signal |

Definition at line 112 of file ahci_dma_wr_fifo.v.

|

Signal |

Definition at line 113 of file ahci_dma_wr_fifo.v.

|

Signal |

Definition at line 114 of file ahci_dma_wr_fifo.v.

|

Signal |

Definition at line 116 of file ahci_dma_wr_fifo.v.

|

Signal |

Definition at line 117 of file ahci_dma_wr_fifo.v.

|

Signal |

Definition at line 118 of file ahci_dma_wr_fifo.v.

|

Signal |

Definition at line 119 of file ahci_dma_wr_fifo.v.

|

Signal |

Definition at line 120 of file ahci_dma_wr_fifo.v.

|

Signal |

Definition at line 122 of file ahci_dma_wr_fifo.v.

|

Signal |

Definition at line 127 of file ahci_dma_wr_fifo.v.

|

Signal |

Definition at line 130 of file ahci_dma_wr_fifo.v.

|

Signal |

Definition at line 132 of file ahci_dma_wr_fifo.v.

|

Module Instance |

Definition at line 289 of file ahci_dma_wr_fifo.v.

|

Module Instance |

Definition at line 300 of file ahci_dma_wr_fifo.v.

|

Module Instance |

Definition at line 312 of file ahci_dma_wr_fifo.v.

The documentation for this Module was generated from the following files:

- x393_sata/ahci/ahci_dma_wr_fifo.v