Public Attributes |

Inputs | |

| mclk | |

| mrst | |

| phase | [ 7 : 0 ] |

| set_phase | |

| load | |

| rst_mmcm | |

| clp_p | |

| clk_n | |

Outputs | |

| ipclk | |

| ipclk2x | |

| ps_rdy | |

| ps_out | [ 7 : 0 ] |

| locked_pxd_mmcm | |

| clkin_pxd_stopped_mmcm | |

| clkfb_pxd_stopped_mmcm | |

Parameters | |

| SENS_PHASE_WIDTH | 8 |

| SENS_BANDWIDTH | "OPTIMIZED" |

| CLKIN_PERIOD_SENSOR | 3 . 000 |

| CLKFBOUT_MULT_SENSOR | 3 |

| CLKFBOUT_PHASE_SENSOR | 0 . 000 |

| IPCLK_PHASE | 0 . 000 |

| IPCLK2X_PHASE | 0 . 000 |

| BUF_IPCLK | "BUFR " |

| BUF_IPCLK2X | "BUFR " |

| SENS_DIVCLK_DIVIDE | 1 |

| SENS_REF_JITTER1 | 0 . 010 |

| SENS_REF_JITTER2 | 0 . 010 |

| SENS_SS_EN | "FALSE" |

| SENS_SS_MODE | "CENTER_HIGH" |

| SENS_SS_MOD_PERIOD | 10000 |

| IODELAY_GRP | "IODELAY_SENSOR" |

| IDELAY_VALUE | integer 0 |

| REFCLK_FREQUENCY | real 200 . 0 |

| HIGH_PERFORMANCE_MODE | "FALSE" |

| HISPI_DELAY_CLK | "FALSE" |

| HISPI_MMCM | "TRUE" |

| HISPI_CAPACITANCE | "DONT_CARE" |

| HISPI_DIFF_TERM | "TRUE" |

| HISPI_UNTUNED_SPLIT | "FALSE" |

| HISPI_DQS_BIAS | "TRUE" |

| HISPI_IBUF_DELAY_VALUE | " 0 " |

| HISPI_IBUF_LOW_PWR | "TRUE" |

| HISPI_IFD_DELAY_VALUE | "AUTO" |

| HISPI_IOSTANDARD | "DIFF_SSTL18_I" |

GENERATE | |

| GENERATE [106] | |

| GENERATE [137] | |

| GENERATE [161] | |

| GENERATE [251] | |

| GENERATE [261] | |

Signals | |

| wire | ipclk_pre |

| wire | ipclk2x_pre |

| wire | clk_fb |

| wire | prst |

| wire | clk_in |

| wire | clk_int |

| wire | set_phase_w |

| wire[ 7 : 0 ] | phase_w |

| wire | ps_rdy_w |

| wire[ 7 : 0 ] | ps_out_w |

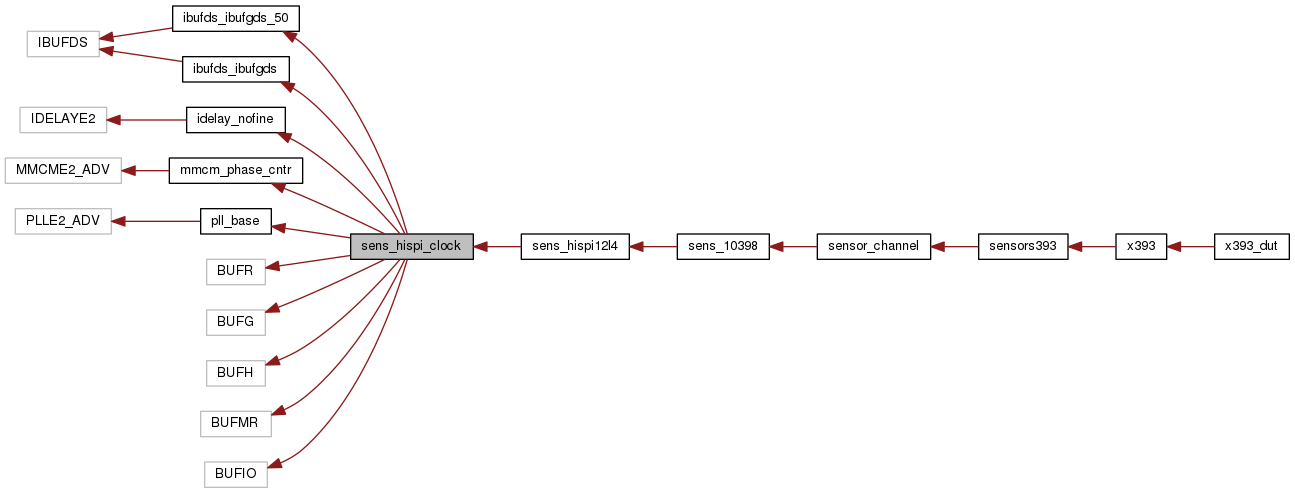

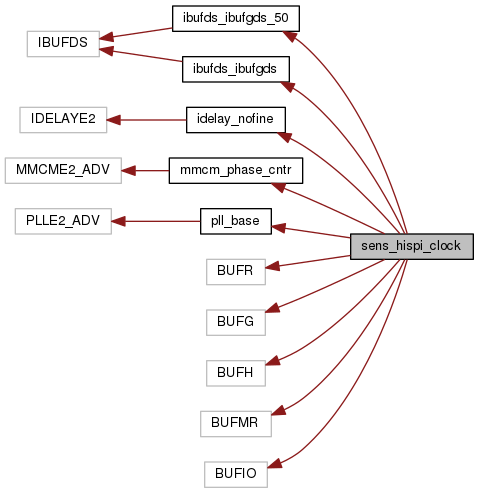

Module Instances | |

| ibufds_ibufgds_50::ibufds_ibufgds0_i | Module ibufds_ibufgds_50 [generate] |

| ibufds_ibufgds::ibufds_ibufgds0_i | Module ibufds_ibufgds [generate] |

| idelay_nofine::clk_dly_i | Module idelay_nofine [generate] |

| mmcm_phase_cntr::mmcm_or_pll_i | Module mmcm_phase_cntr [generate] |

| pll_base::mmcm_or_pll_i | Module pll_base [generate] |

| BUFR::clk1x_i | Module BUFR [generate] |

| BUFG::clk1x_i | Module BUFG [generate] |

| BUFH::clk1x_i | Module BUFH [generate] |

| BUFMR::clk1x_i | Module BUFMR [generate] |

| BUFIO::clk1x_i | Module BUFIO [generate] |

| BUFG::clk2x_i | Module BUFG [generate] |

| BUFH::clk2x_i | Module BUFH [generate] |

| BUFR::clk2x_i | Module BUFR [generate] |

| BUFMR::clk2x_i | Module BUFMR [generate] |

| BUFIO::clk2x_i | Module BUFIO [generate] |

Detailed Description

Definition at line 41 of file sens_hispi_clock.v.

Member Data Documentation

|

Parameter |

Definition at line 43 of file sens_hispi_clock.v.

|

Parameter |

Definition at line 44 of file sens_hispi_clock.v.

|

Parameter |

Definition at line 45 of file sens_hispi_clock.v.

|

Parameter |

Definition at line 46 of file sens_hispi_clock.v.

|

Parameter |

Definition at line 47 of file sens_hispi_clock.v.

|

Parameter |

Definition at line 48 of file sens_hispi_clock.v.

|

Parameter |

Definition at line 49 of file sens_hispi_clock.v.

Definition at line 50 of file sens_hispi_clock.v.

|

Parameter |

Definition at line 51 of file sens_hispi_clock.v.

|

Parameter |

Definition at line 53 of file sens_hispi_clock.v.

|

Parameter |

Definition at line 54 of file sens_hispi_clock.v.

|

Parameter |

Definition at line 55 of file sens_hispi_clock.v.

|

Parameter |

Definition at line 56 of file sens_hispi_clock.v.

|

Parameter |

Definition at line 57 of file sens_hispi_clock.v.

|

Parameter |

Definition at line 58 of file sens_hispi_clock.v.

|

Parameter |

Definition at line 60 of file sens_hispi_clock.v.

|

Parameter |

Definition at line 61 of file sens_hispi_clock.v.

|

Parameter |

Definition at line 62 of file sens_hispi_clock.v.

|

Parameter |

Definition at line 63 of file sens_hispi_clock.v.

|

Parameter |

Definition at line 65 of file sens_hispi_clock.v.

|

Parameter |

Definition at line 66 of file sens_hispi_clock.v.

|

Parameter |

Definition at line 67 of file sens_hispi_clock.v.

|

Parameter |

Definition at line 68 of file sens_hispi_clock.v.

|

Parameter |

Definition at line 69 of file sens_hispi_clock.v.

|

Parameter |

Definition at line 70 of file sens_hispi_clock.v.

|

Parameter |

Definition at line 71 of file sens_hispi_clock.v.

|

Parameter |

Definition at line 72 of file sens_hispi_clock.v.

|

Parameter |

Definition at line 73 of file sens_hispi_clock.v.

|

Parameter |

Definition at line 74 of file sens_hispi_clock.v.

|

Input |

Definition at line 77 of file sens_hispi_clock.v.

|

Input |

Definition at line 78 of file sens_hispi_clock.v.

|

Input |

Definition at line 79 of file sens_hispi_clock.v.

|

Input |

Definition at line 80 of file sens_hispi_clock.v.

|

Input |

Definition at line 81 of file sens_hispi_clock.v.

|

Input |

Definition at line 82 of file sens_hispi_clock.v.

|

Input |

Definition at line 83 of file sens_hispi_clock.v.

|

Input |

Definition at line 84 of file sens_hispi_clock.v.

|

Output |

Definition at line 85 of file sens_hispi_clock.v.

|

Output |

Definition at line 86 of file sens_hispi_clock.v.

|

Output |

Definition at line 87 of file sens_hispi_clock.v.

|

Output |

Definition at line 88 of file sens_hispi_clock.v.

|

Output |

Definition at line 89 of file sens_hispi_clock.v.

|

Output |

Definition at line 90 of file sens_hispi_clock.v.

|

Output |

Definition at line 91 of file sens_hispi_clock.v.

|

Signal |

Definition at line 93 of file sens_hispi_clock.v.

|

Signal |

Definition at line 94 of file sens_hispi_clock.v.

|

Signal |

Definition at line 95 of file sens_hispi_clock.v.

|

Signal |

Definition at line 96 of file sens_hispi_clock.v.

|

Signal |

Definition at line 97 of file sens_hispi_clock.v.

|

Signal |

Definition at line 98 of file sens_hispi_clock.v.

|

Signal |

Definition at line 99 of file sens_hispi_clock.v.

|

Signal |

Definition at line 100 of file sens_hispi_clock.v.

|

Signal |

Definition at line 101 of file sens_hispi_clock.v.

|

Signal |

Definition at line 102 of file sens_hispi_clock.v.

|

Module Instance |

Definition at line 253 of file sens_hispi_clock.v.

|

Module Instance |

Definition at line 262 of file sens_hispi_clock.v.

|

Module Instance |

Definition at line 254 of file sens_hispi_clock.v.

|

Module Instance |

Definition at line 263 of file sens_hispi_clock.v.

|

Module Instance |

Definition at line 257 of file sens_hispi_clock.v.

|

Module Instance |

Definition at line 266 of file sens_hispi_clock.v.

|

Module Instance |

Definition at line 256 of file sens_hispi_clock.v.

|

Module Instance |

Definition at line 265 of file sens_hispi_clock.v.

|

Module Instance |

Definition at line 252 of file sens_hispi_clock.v.

|

Module Instance |

Definition at line 264 of file sens_hispi_clock.v.

|

GENERATE |

Definition at line 106 of file sens_hispi_clock.v.

|

GENERATE |

Definition at line 137 of file sens_hispi_clock.v.

|

GENERATE |

Definition at line 161 of file sens_hispi_clock.v.

|

GENERATE |

Definition at line 251 of file sens_hispi_clock.v.

|

GENERATE |

Definition at line 261 of file sens_hispi_clock.v.

|

Module Instance |

Definition at line 122 of file sens_hispi_clock.v.

|

Module Instance |

Definition at line 108 of file sens_hispi_clock.v.

|

Module Instance |

Definition at line 139 of file sens_hispi_clock.v.

|

Module Instance |

Definition at line 163 of file sens_hispi_clock.v.

|

Module Instance |

Definition at line 217 of file sens_hispi_clock.v.

The documentation for this Module was generated from the following files:

- sensor/sens_hispi_clock.v