phy_top Module Reference

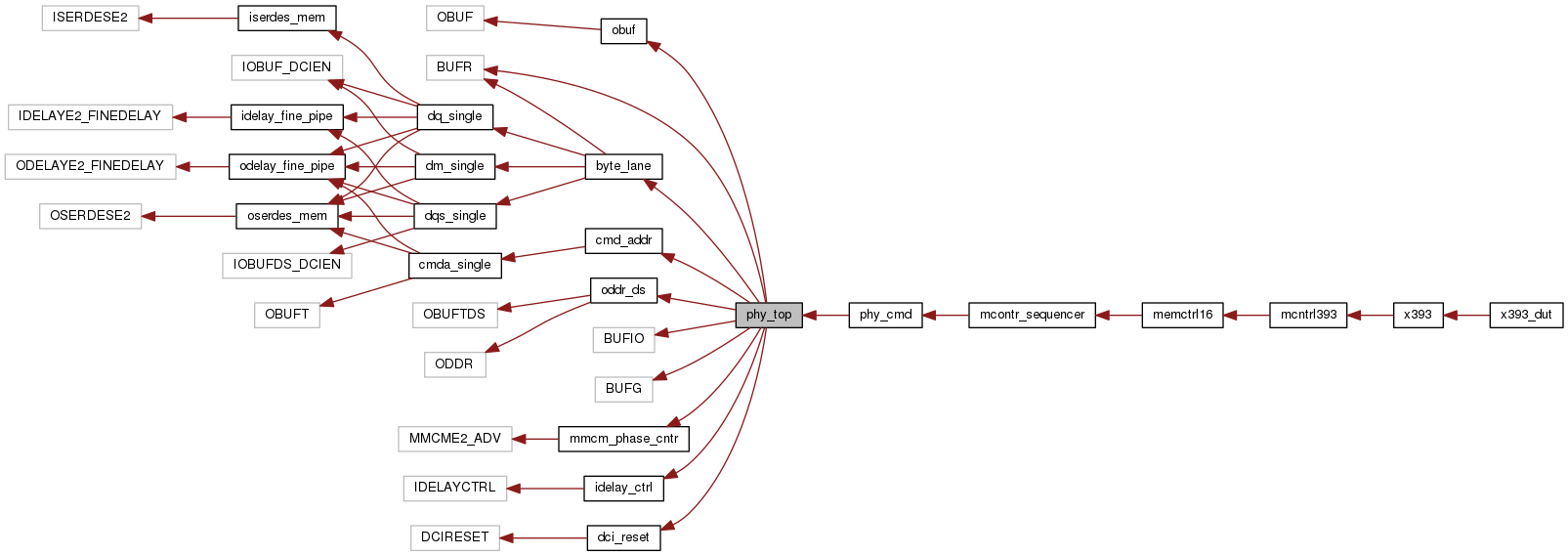

Inheritance diagram for phy_top:

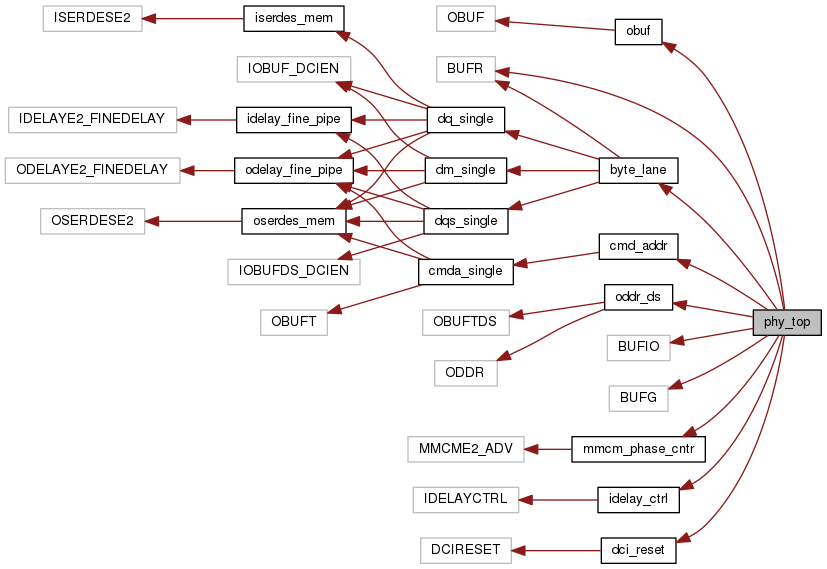

Collaboration diagram for phy_top:

Static Public Member Functions |

Always Constructs | |

| ALWAYS_328 | ( clk_div ) |

| ALWAYS_329 | ( mclk ) |

| ALWAYS_330 | ( clk_div ) |

Public Attributes |

Inputs | |

| clk_in | |

| mrst | |

| ref_clk | |

| rst_in | |

| ddr_rst | |

| dci_rst | |

| dly_rst | |

| in_a | [ 2 *ADDRESS_NUMBER - 1 : 0 ] |

| in_ba | [ 5 : 0 ] |

| in_we | [ 1 : 0 ] |

| in_ras | [ 1 : 0 ] |

| in_cas | [ 1 : 0 ] |

| in_cke | [ 1 : 0 ] |

| in_odt | [ 1 : 0 ] |

| in_tri | |

| din | [ 63 : 0 ] |

| din_dm | [ 7 : 0 ] |

| tin_dq | [ 7 : 0 ] |

| din_dqs | [ 7 : 0 ] |

| tin_dqs | [ 7 : 0 ] |

| inv_clk_div | |

| dci_disable_dqs | |

| dci_disable_dq | |

| dly_data | [ 7 : 0 ] |

| dly_addr | [ 6 : 0 ] |

| ld_delay | |

| set | |

Inouts | |

| dq | [ 15 : 0 ] |

| dqsl | |

| ndqsl | |

| dqsu | |

| ndqsu | |

Outputs | |

| ddr3_nrst | |

| ddr3_clk | |

| ddr3_nclk | |

| ddr3_a | [ADDRESS_NUMBER - 1 : 0 ] |

| ddr3_ba | [ 2 : 0 ] |

| ddr3_we | |

| ddr3_ras | |

| ddr3_cas | |

| ddr3_cke | |

| ddr3_odt | |

| dml | |

| dmu | |

| clk | |

| clk_div | |

| mclk | |

| idelay_ctrl_reset | |

| dout | [ 63 : 0 ] |

| locked_mmcm | |

| locked_pll | |

| dly_ready | |

| dci_ready | |

| tmp_debug | [ 7 : 0 ] |

| ps_rdy | |

| ps_out | [PHASE_WIDTH - 1 : 0 ] |

Parameters | |

| IOSTANDARD_DQ | "SSTL15_T_DCI" |

| IOSTANDARD_DM | "SSTL15" |

| IOSTANDARD_DQS | "DIFF_SSTL15_T_DCI" |

| IOSTANDARD_CMDA | "SSTL15" |

| IOSTANDARD_CLK | "DIFF_SSTL15" |

| SLEW_DQ | "SLOW" |

| SLEW_DQS | "SLOW" |

| SLEW_CMDA | "SLOW" |

| SLEW_CLK | "SLOW" |

| IBUF_LOW_PWR | "TRUE" |

| IODELAY_GRP | "IODELAY_MEMORY" |

| REFCLK_FREQUENCY | real 300 . 0 |

| HIGH_PERFORMANCE_MODE | "FALSE" |

| ADDRESS_NUMBER | integer 15 |

| PHASE_WIDTH | 8 |

| BANDWIDTH | "OPTIMIZED" |

| CLKIN_PERIOD | 10 |

| CLKFBOUT_MULT | 8 |

| DIVCLK_DIVIDE | 1 |

| CLKFBOUT_USE_FINE_PS | 1 |

| CLKFBOUT_PHASE | 0 . 000 |

| SDCLK_PHASE | 0 . 000 |

| CLK_PHASE | 0 . 000 |

| CLK_DIV_PHASE | 0 . 000 |

| MCLK_PHASE | 90 . 000 |

| REF_JITTER1 | 0 . 010 |

| SS_EN | "FALSE" |

| SS_MODE | "CENTER_HIGH" |

| SS_MOD_PERIOD | 10000 |

Signals | |

| reg | rst |

| wire | ld_data_l |

| wire | ld_data_h |

| wire | ld_cmda |

| wire | ld_mmcm |

| wire | clkin_stopped_mmcm |

| wire | clkfb_stopped_mmcm |

| reg | dbg1 |

| reg | dbg2 |

| wire | sdclk |

| wire | clk_pre |

| wire | clk_div_pre |

| wire | sdclk_pre |

| wire | mclk_pre |

| wire | clk_fb |

Module Instances | |

| obuf::obuf_i | Module obuf |

| cmd_addr::cmd_addr_i | Module cmd_addr |

| byte_lane::byte_lane0_i | Module byte_lane |

| byte_lane::byte_lane1_i | Module byte_lane |

| oddr_ds::oddr_ds_i | Module oddr_ds |

| BUFR::clk_bufr_i | Module BUFR |

| BUFR::clk_div_bufr_i | Module BUFR |

| BUFIO::iclk_bufio_i | Module BUFIO |

| BUFG::mclk_i | Module BUFG |

| mmcm_phase_cntr::mmcm_phase_cntr_i | Module mmcm_phase_cntr |

| idelay_ctrl::idelay_ctrl_i | Module idelay_ctrl |

| dci_reset::dci_reset_i | Module dci_reset |

Detailed Description

Member Function Documentation

Member Data Documentation

|

Parameter |

|

Parameter |

|

Parameter |

|

Parameter |

|

Parameter |

|

Parameter |

|

Parameter |

|

Parameter |

|

Parameter |

|

Parameter |

|

Parameter |

|

Parameter |

|

Parameter |

|

Parameter |

|

Parameter |

|

Parameter |

|

Parameter |

|

Parameter |

|

Parameter |

|

Parameter |

|

Parameter |

|

Output |

|

Output |

|

Input |

|

Input |

|

Input |

|

Input |

|

Output |

|

Output |

|

Output |

|

Signal |

|

Signal |

|

Signal |

|

Module Instance |

|

Module Instance |

The documentation for this Module was generated from the following files:

- memctrl/phy/phy_top.v