Static Public Member Functions |

Always Constructs | |

| ALWAYS_546 | ( rst or clk ) |

Public Attributes |

Inputs | |

| rst | |

| clk | |

| srst | |

| db_in0 | [ 7 : 0 ] |

| rq_in0 | |

| db_in1 | [ 7 : 0 ] |

| rq_in1 | |

| start_out | |

Outputs | |

| start_in0 | |

| start_in1 | |

| db_out | [ 7 : 0 ] |

| rq_out | |

Parameters | |

| FIFO_TYPE | "ONE_CYCLE" |

GENERATE | |

| GENERATE [122] | |

Signals | |

| wire[ 1 : 0 ] | rq_in |

| wire[ 1 : 0 ] | start_rcv |

| reg[ 1 : 0 ] | rcv_rest_r |

| wire[ 1 : 0 ] | fifo_half_full |

| wire[ 7 : 0 ] | fifo0_out |

| wire[ 7 : 0 ] | fifo1_out |

| wire[ 1 : 0 ] | fifo_last_byte |

| wire[ 1 : 0 ] | fifo_nempty_pre |

| wire[ 1 : 0 ] | fifo_nempty |

| wire[ 1 : 0 ] | fifo_re |

| reg | next_chn |

| reg | current_chn_r |

| reg | snd_rest_r |

| wire | snd_pre_start |

| wire | snd_last_byte |

| wire | chn_sel_w |

| wire | early_chn |

| wire | set_other_only_w |

Module Instances | |

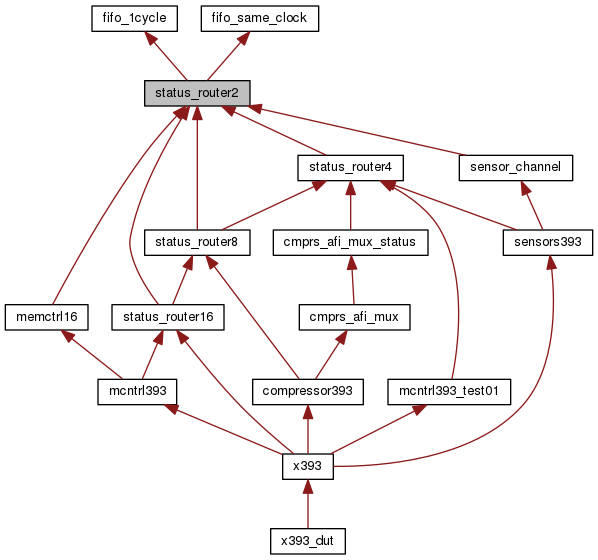

| fifo_1cycle::fifo_in0_i | Module fifo_1cycle [generate] |

| fifo_1cycle::fifo_in1_i | Module fifo_1cycle [generate] |

| fifo_same_clock::fifo_in0_i | Module fifo_same_clock [generate] |

| fifo_same_clock::fifo_in1_i | Module fifo_same_clock [generate] |

Detailed Description

Definition at line 43 of file status_router2.v.

Member Function Documentation

Definition at line 100 of file status_router2.v.

Member Data Documentation

|

Parameter |

Definition at line 44 of file status_router2.v.

|

Input |

Definition at line 46 of file status_router2.v.

|

Input |

Definition at line 47 of file status_router2.v.

|

Input |

Definition at line 48 of file status_router2.v.

|

Input |

Definition at line 50 of file status_router2.v.

|

Input |

Definition at line 51 of file status_router2.v.

|

Output |

Definition at line 52 of file status_router2.v.

|

Input |

Definition at line 53 of file status_router2.v.

|

Input |

Definition at line 54 of file status_router2.v.

|

Output |

Definition at line 55 of file status_router2.v.

|

Output |

Definition at line 57 of file status_router2.v.

|

Output |

Definition at line 58 of file status_router2.v.

|

Input |

Definition at line 59 of file status_router2.v.

|

Signal |

Definition at line 61 of file status_router2.v.

|

Signal |

Definition at line 62 of file status_router2.v.

|

Signal |

Definition at line 63 of file status_router2.v.

|

Signal |

Definition at line 64 of file status_router2.v.

|

Signal |

Definition at line 70 of file status_router2.v.

|

Signal |

Definition at line 71 of file status_router2.v.

|

Signal |

Definition at line 72 of file status_router2.v.

|

Signal |

Definition at line 73 of file status_router2.v.

|

Signal |

Definition at line 74 of file status_router2.v.

|

Signal |

Definition at line 75 of file status_router2.v.

|

Signal |

Definition at line 76 of file status_router2.v.

|

Signal |

Definition at line 77 of file status_router2.v.

|

Signal |

Definition at line 78 of file status_router2.v.

|

Signal |

Definition at line 79 of file status_router2.v.

|

Signal |

Definition at line 80 of file status_router2.v.

|

Signal |

Definition at line 81 of file status_router2.v.

|

Signal |

Definition at line 82 of file status_router2.v.

|

Signal |

Definition at line 83 of file status_router2.v.

|

Module Instance |

Definition at line 124 of file status_router2.v.

|

Module Instance |

Definition at line 140 of file status_router2.v.

|

Module Instance |

Definition at line 156 of file status_router2.v.

|

Module Instance |

Definition at line 172 of file status_router2.v.

|

GENERATE |

Definition at line 122 of file status_router2.v.

The documentation for this Module was generated from the following files:

- util_modules/status_router2.v