Public Attributes |

Inputs | |

| clk | |

| reset | |

| wid_in | [ID_WIDTH - 1 : 0 ] |

| wdata_in | [DATA_WIDTH - 1 : 0 ] |

| wstrb_in | [WSTB_WIDTH - 1 : 0 ] |

| wlast_in | |

| wready | |

| set_cmd | |

Outputs | |

| wid | [ID_WIDTH - 1 : 0 ] |

| wdata | [DATA_WIDTH - 1 : 0 ] |

| wstrb | [WSTB_WIDTH - 1 : 0 ] |

| wlast | |

| wvalid | |

| ready | |

Parameters | |

| ID_WIDTH | integer 12 |

| DATA_WIDTH | integer 32 |

| WSTB_WIDTH | integer 4 |

| LATENCY | integer 0 |

| DEPTH | integer 8 |

| DATA_DELAY | 3 . 5 |

| VALID_DELAY | 4 . 0 |

Signals | |

| wire[ID_WIDTH - 1 : 0 ] | wid_out |

| wire[DATA_WIDTH - 1 : 0 ] | wdata_out |

| wire[WSTB_WIDTH - 1 : 0 ] | wstrb_out |

| wire | wlast_out |

| wire | wvalid_out |

Module Instances | |

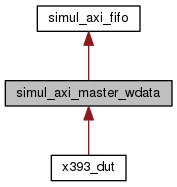

| simul_axi_fifo::simul_axi_fifo_i | Module simul_axi_fifo |

Detailed Description

Definition at line 41 of file simul_axi_master_wdata.v.

Member Data Documentation

|

Parameter |

Definition at line 42 of file simul_axi_master_wdata.v.

|

Parameter |

Definition at line 43 of file simul_axi_master_wdata.v.

|

Parameter |

Definition at line 44 of file simul_axi_master_wdata.v.

|

Parameter |

Definition at line 45 of file simul_axi_master_wdata.v.

|

Parameter |

Definition at line 46 of file simul_axi_master_wdata.v.

|

Parameter |

Definition at line 47 of file simul_axi_master_wdata.v.

|

Parameter |

Definition at line 48 of file simul_axi_master_wdata.v.

|

Input |

Definition at line 50 of file simul_axi_master_wdata.v.

|

Input |

Definition at line 51 of file simul_axi_master_wdata.v.

Definition at line 52 of file simul_axi_master_wdata.v.

|

Input |

Definition at line 53 of file simul_axi_master_wdata.v.

|

Input |

Definition at line 54 of file simul_axi_master_wdata.v.

|

Input |

Definition at line 55 of file simul_axi_master_wdata.v.

Definition at line 56 of file simul_axi_master_wdata.v.

|

Output |

Definition at line 57 of file simul_axi_master_wdata.v.

|

Output |

Definition at line 58 of file simul_axi_master_wdata.v.

|

Output |

Definition at line 59 of file simul_axi_master_wdata.v.

|

Output |

Definition at line 60 of file simul_axi_master_wdata.v.

|

Input |

Definition at line 61 of file simul_axi_master_wdata.v.

|

Input |

Definition at line 63 of file simul_axi_master_wdata.v.

|

Output |

Definition at line 64 of file simul_axi_master_wdata.v.

|

Signal |

Definition at line 67 of file simul_axi_master_wdata.v.

|

Signal |

Definition at line 68 of file simul_axi_master_wdata.v.

|

Signal |

Definition at line 69 of file simul_axi_master_wdata.v.

|

Signal |

Definition at line 70 of file simul_axi_master_wdata.v.

|

Signal |

Definition at line 71 of file simul_axi_master_wdata.v.

|

Module Instance |

Definition at line 79 of file simul_axi_master_wdata.v.

The documentation for this Module was generated from the following files:

- simulation_modules/simul_axi_master_wdata.v