Static Public Member Functions |

Always Constructs | |

| ALWAYS_366 | ( pclk ) |

| ALWAYS_367 | ( mclk ) |

| ALWAYS_368 | ( pclk ) |

| ALWAYS_369 | ( pclk ) |

| ALWAYS_370 | ( pclk ) |

| ALWAYS_371 | ( mclk ) |

| ALWAYS_372 | ( pclk ) |

Public Attributes |

Inputs | |

| mrst | |

| prst | |

| pclk | |

| sof | |

| eof | |

| hact | |

| hist_di | [ 7 : 0 ] |

| mclk | |

| hist_en | |

| hist_rst | |

| hist_grant | |

| cmd_ad | [ 7 : 0 ] |

| cmd_stb | |

| debug_sl | |

| debug_di | |

Outputs | |

| hist_rq | |

| hist_do | [ 31 : 0 ] |

| hist_dv | reg |

| debug_do | |

Parameters | |

| HISTOGRAM_RAM_MODE | "BUF32" |

| HISTOGRAM_ADDR | 'h33c |

| HISTOGRAM_ADDR_MASK | 'h7fe |

| HISTOGRAM_LEFT_TOP | 'h0 |

| HISTOGRAM_WIDTH_HEIGHT | 'h1 |

| 7492 | |

| 7493 | |

| HIST_WIDTH | (HISTOGRAM_RAM_MODE == "BUF18") ? 18 : 32 |

GENERATE | |

| GENERATE [514] | |

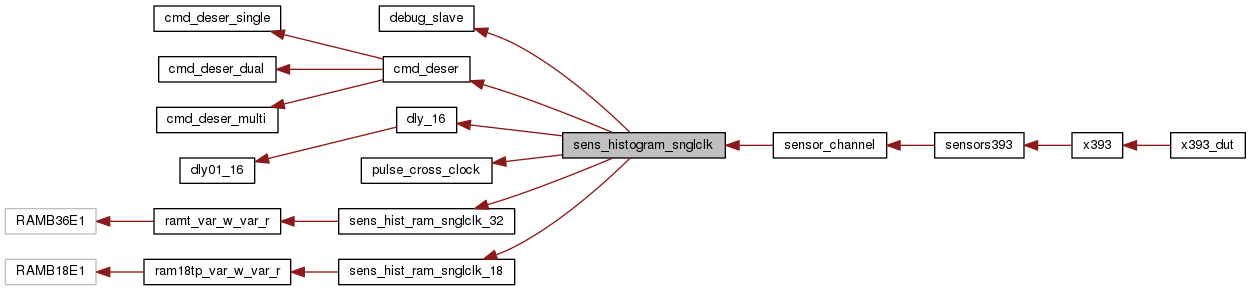

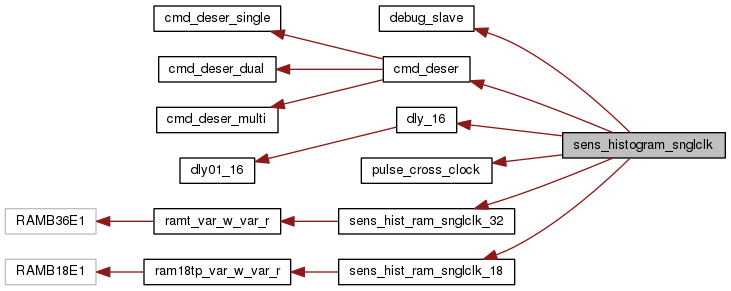

Detailed Description

Definition at line 43 of file sens_histogram_snglclk.v.

Member Function Documentation

|

Always Construct |

Definition at line 161 of file sens_histogram_snglclk.v.

|

Always Construct |

Definition at line 169 of file sens_histogram_snglclk.v.

|

Always Construct |

Definition at line 174 of file sens_histogram_snglclk.v.

|

Always Construct |

Definition at line 180 of file sens_histogram_snglclk.v.

|

Always Construct |

Definition at line 279 of file sens_histogram_snglclk.v.

|

Always Construct |

Definition at line 328 of file sens_histogram_snglclk.v.

|

Always Construct |

Definition at line 369 of file sens_histogram_snglclk.v.

Member Data Documentation

|

Parameter |

Definition at line 44 of file sens_histogram_snglclk.v.

|

Parameter |

Definition at line 45 of file sens_histogram_snglclk.v.

|

Parameter |

Definition at line 46 of file sens_histogram_snglclk.v.

|

Parameter |

Definition at line 47 of file sens_histogram_snglclk.v.

|

Parameter |

Definition at line 48 of file sens_histogram_snglclk.v.

|

Parameter |

Definition at line 49 of file sens_histogram_snglclk.v.

|

Parameter |

Definition at line 51 of file sens_histogram_snglclk.v.

|

Input |

Definition at line 55 of file sens_histogram_snglclk.v.

|

Input |

Definition at line 56 of file sens_histogram_snglclk.v.

|

Input |

Definition at line 57 of file sens_histogram_snglclk.v.

|

Input |

Definition at line 59 of file sens_histogram_snglclk.v.

|

Input |

Definition at line 60 of file sens_histogram_snglclk.v.

|

Input |

Definition at line 61 of file sens_histogram_snglclk.v.

|

Input |

Definition at line 62 of file sens_histogram_snglclk.v.

|

Input |

Definition at line 64 of file sens_histogram_snglclk.v.

|

Input |

Definition at line 65 of file sens_histogram_snglclk.v.

|

Input |

Definition at line 66 of file sens_histogram_snglclk.v.

|

Output |

Definition at line 67 of file sens_histogram_snglclk.v.

|

Input |

Definition at line 68 of file sens_histogram_snglclk.v.

|

Output |

Definition at line 69 of file sens_histogram_snglclk.v.

|

Output |

Definition at line 70 of file sens_histogram_snglclk.v.

|

Input |

Definition at line 71 of file sens_histogram_snglclk.v.

|

Input |

Definition at line 72 of file sens_histogram_snglclk.v.

|

Output |

Definition at line 75 of file sens_histogram_snglclk.v.

|

Input |

Definition at line 76 of file sens_histogram_snglclk.v.

|

Input |

Definition at line 77 of file sens_histogram_snglclk.v.

|

Parameter |

Definition at line 81 of file sens_histogram_snglclk.v.

|

Signal |

Definition at line 82 of file sens_histogram_snglclk.v.

|

Signal |

Definition at line 84 of file sens_histogram_snglclk.v.

|

Signal |

Definition at line 85 of file sens_histogram_snglclk.v.

|

Signal |

Definition at line 87 of file sens_histogram_snglclk.v.

|

Signal |

Definition at line 89 of file sens_histogram_snglclk.v.

|

Signal |

Definition at line 90 of file sens_histogram_snglclk.v.

|

Signal |

Definition at line 92 of file sens_histogram_snglclk.v.

|

Signal |

Definition at line 93 of file sens_histogram_snglclk.v.

|

Signal |

Definition at line 94 of file sens_histogram_snglclk.v.

|

Signal |

Definition at line 96 of file sens_histogram_snglclk.v.

|

Signal |

Definition at line 97 of file sens_histogram_snglclk.v.

|

Signal |

Definition at line 98 of file sens_histogram_snglclk.v.

|

Signal |

Definition at line 99 of file sens_histogram_snglclk.v.

|

Signal |

Definition at line 100 of file sens_histogram_snglclk.v.

|

Signal |

Definition at line 101 of file sens_histogram_snglclk.v.

|

Signal |

Definition at line 103 of file sens_histogram_snglclk.v.

|

Signal |

Definition at line 104 of file sens_histogram_snglclk.v.

|

Signal |

Definition at line 105 of file sens_histogram_snglclk.v.

|

Signal |

Definition at line 106 of file sens_histogram_snglclk.v.

|

Signal |

Definition at line 108 of file sens_histogram_snglclk.v.

|

Signal |

Definition at line 110 of file sens_histogram_snglclk.v.

|

Signal |

Definition at line 111 of file sens_histogram_snglclk.v.

|

Signal |

Definition at line 113 of file sens_histogram_snglclk.v.

|

Signal |

Definition at line 115 of file sens_histogram_snglclk.v.

|

Signal |

Definition at line 117 of file sens_histogram_snglclk.v.

|

Signal |

Definition at line 119 of file sens_histogram_snglclk.v.

|

Signal |

Definition at line 120 of file sens_histogram_snglclk.v.

|

Signal |

Definition at line 121 of file sens_histogram_snglclk.v.

|

Signal |

Definition at line 122 of file sens_histogram_snglclk.v.

|

Signal |

Definition at line 123 of file sens_histogram_snglclk.v.

|

Signal |

Definition at line 125 of file sens_histogram_snglclk.v.

|

Signal |

Definition at line 126 of file sens_histogram_snglclk.v.

|

Signal |

Definition at line 127 of file sens_histogram_snglclk.v.

|

Signal |

Definition at line 128 of file sens_histogram_snglclk.v.

|

Signal |

Definition at line 129 of file sens_histogram_snglclk.v.

|

Signal |

Definition at line 131 of file sens_histogram_snglclk.v.

|

Signal |

Definition at line 132 of file sens_histogram_snglclk.v.

|

Signal |

Definition at line 133 of file sens_histogram_snglclk.v.

|

Signal |

Definition at line 134 of file sens_histogram_snglclk.v.

|

Signal |

Definition at line 135 of file sens_histogram_snglclk.v.

|

Signal |

Definition at line 136 of file sens_histogram_snglclk.v.

|

Signal |

Definition at line 137 of file sens_histogram_snglclk.v.

|

Signal |

Definition at line 138 of file sens_histogram_snglclk.v.

|

Signal |

Definition at line 139 of file sens_histogram_snglclk.v.

|

Signal |

Definition at line 140 of file sens_histogram_snglclk.v.

|

Signal |

Definition at line 141 of file sens_histogram_snglclk.v.

|

Signal |

Definition at line 144 of file sens_histogram_snglclk.v.

|

Signal |

Definition at line 145 of file sens_histogram_snglclk.v.

|

Signal |

Definition at line 156 of file sens_histogram_snglclk.v.

|

Signal |

Definition at line 157 of file sens_histogram_snglclk.v.

|

Signal |

Definition at line 158 of file sens_histogram_snglclk.v.

|

Signal |

Definition at line 243 of file sens_histogram_snglclk.v.

|

Signal |

Definition at line 244 of file sens_histogram_snglclk.v.

|

Signal |

Definition at line 245 of file sens_histogram_snglclk.v.

|

Signal |

Definition at line 246 of file sens_histogram_snglclk.v.

|

Signal |

Definition at line 247 of file sens_histogram_snglclk.v.

|

Signal |

Definition at line 248 of file sens_histogram_snglclk.v.

|

Signal |

Definition at line 249 of file sens_histogram_snglclk.v.

|

Signal |

Definition at line 250 of file sens_histogram_snglclk.v.

|

Signal |

Definition at line 251 of file sens_histogram_snglclk.v.

|

Signal |

Definition at line 252 of file sens_histogram_snglclk.v.

|

Signal |

Definition at line 254 of file sens_histogram_snglclk.v.

|

Signal |

Definition at line 255 of file sens_histogram_snglclk.v.

|

Signal |

Definition at line 257 of file sens_histogram_snglclk.v.

|

Signal |

Definition at line 258 of file sens_histogram_snglclk.v.

|

Signal |

Definition at line 259 of file sens_histogram_snglclk.v.

|

Signal |

Definition at line 260 of file sens_histogram_snglclk.v.

|

Signal |

Definition at line 262 of file sens_histogram_snglclk.v.

|

Signal |

Definition at line 263 of file sens_histogram_snglclk.v.

|

Signal |

Definition at line 264 of file sens_histogram_snglclk.v.

|

Signal |

Definition at line 265 of file sens_histogram_snglclk.v.

|

Signal |

Definition at line 266 of file sens_histogram_snglclk.v.

|

Signal |

Definition at line 267 of file sens_histogram_snglclk.v.

|

Signal |

Definition at line 268 of file sens_histogram_snglclk.v.

|

Signal |

Definition at line 269 of file sens_histogram_snglclk.v.

|

Signal |

Definition at line 270 of file sens_histogram_snglclk.v.

|

Signal |

Definition at line 271 of file sens_histogram_snglclk.v.

|

Signal |

Definition at line 272 of file sens_histogram_snglclk.v.

|

Signal |

Definition at line 273 of file sens_histogram_snglclk.v.

|

Signal |

Definition at line 274 of file sens_histogram_snglclk.v.

|

Signal |

Definition at line 326 of file sens_histogram_snglclk.v.

|

Module Instance |

Definition at line 394 of file sens_histogram_snglclk.v.

|

Module Instance |

Definition at line 377 of file sens_histogram_snglclk.v.

|

Module Instance |

Definition at line 415 of file sens_histogram_snglclk.v.

|

Module Instance |

Definition at line 425 of file sens_histogram_snglclk.v.

|

Module Instance |

Definition at line 435 of file sens_histogram_snglclk.v.

|

Module Instance |

Definition at line 445 of file sens_histogram_snglclk.v.

|

Module Instance |

Definition at line 455 of file sens_histogram_snglclk.v.

|

Module Instance |

Definition at line 465 of file sens_histogram_snglclk.v.

|

GENERATE |

Definition at line 514 of file sens_histogram_snglclk.v.

|

Module Instance |

Definition at line 476 of file sens_histogram_snglclk.v.

|

Module Instance |

Definition at line 485 of file sens_histogram_snglclk.v.

|

Module Instance |

Definition at line 494 of file sens_histogram_snglclk.v.

|

Module Instance |

Definition at line 503 of file sens_histogram_snglclk.v.

|

Module Instance |

Definition at line 536 of file sens_histogram_snglclk.v.

|

Module Instance |

Definition at line 516 of file sens_histogram_snglclk.v.

The documentation for this Module was generated from the following files:

- sensor/sens_histogram_snglclk.v