phy_cmd Module Reference

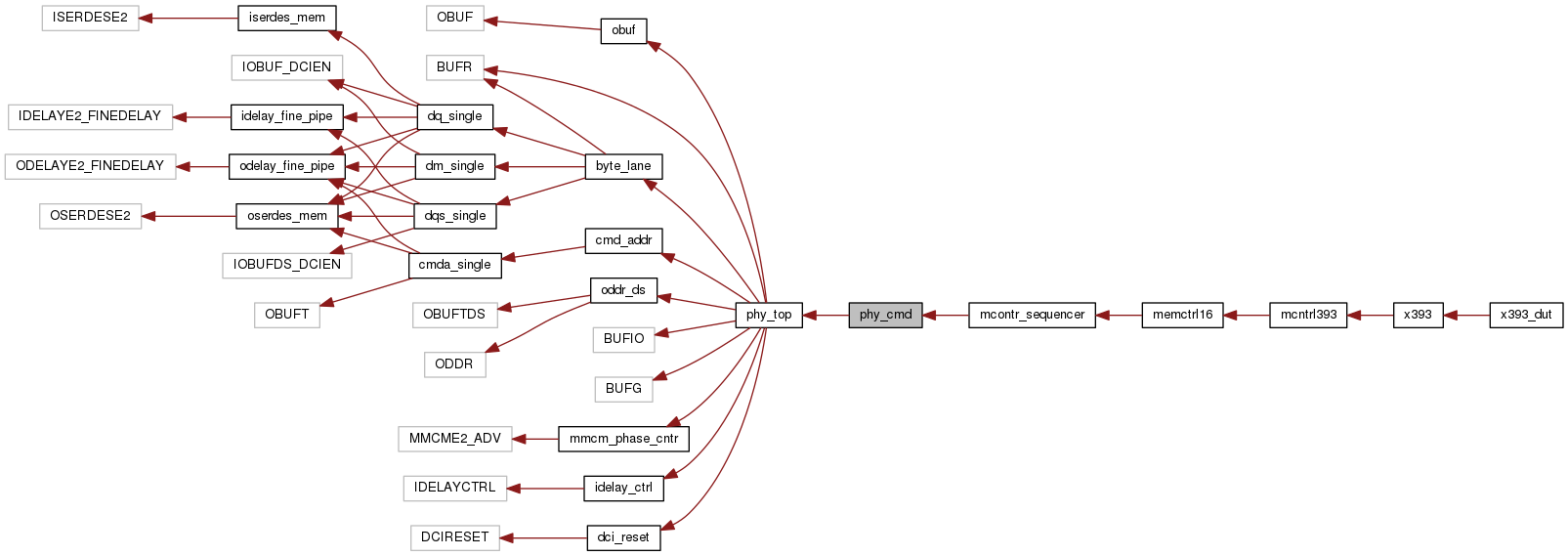

Inheritance diagram for phy_cmd:

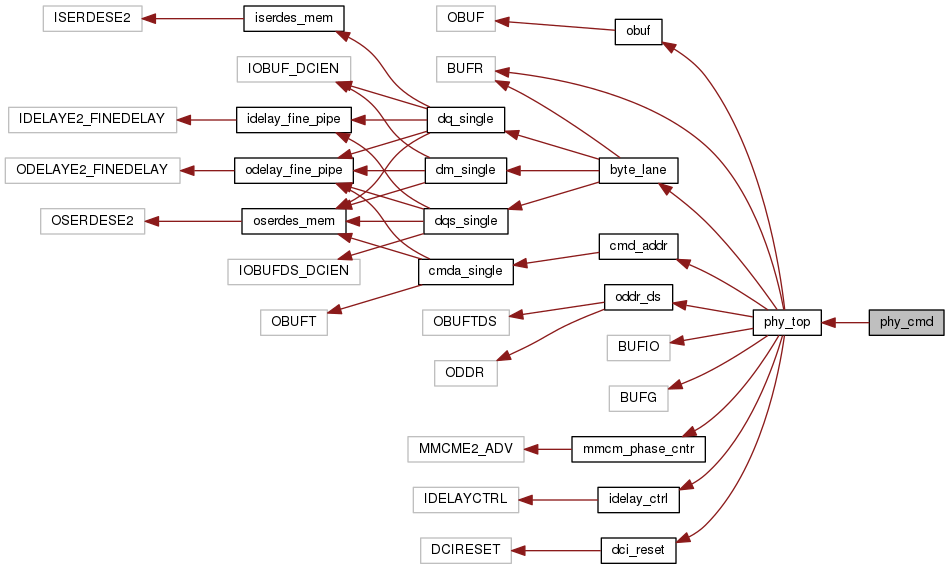

Collaboration diagram for phy_cmd:

Static Public Member Functions |

Always Constructs | |

| ALWAYS_321 | ( mclk ) |

| ALWAYS_322 | ( mclk ) |

| ALWAYS_323 | ( clk_div ) |

| ALWAYS_324 | ( clk_div ) |

| ALWAYS_325 | ( clk_div ) |

| ALWAYS_326 | ( mclk ) |

| ALWAYS_327 | ( mclk ) |

Public Attributes |

Inputs | |

| clk_in | |

| rst_in | |

| mrst | |

| ref_clk | |

| dly_data | [ 7 : 0 ] |

| dly_addr | [ 6 : 0 ] |

| ld_delay | |

| set | |

| phy_cmd_word | [ 31 : 0 ] |

| add_pause | |

| buf_rdata | [ 63 : 0 ] |

| cmda_en | |

| ddr_rst | |

| dci_rst | |

| dly_rst | |

| ddr_cke | |

| inv_clk_div | |

| dqs_pattern | [ 7 : 0 ] |

| dqm_pattern | [ 7 : 0 ] |

| dq_tri_on_pattern | [ 3 : 0 ] |

| dq_tri_off_pattern | [ 3 : 0 ] |

| dqs_tri_on_pattern | [ 3 : 0 ] |

| dqs_tri_off_pattern | [ 3 : 0 ] |

Inouts | |

| SDD | [ 15 : 0 ] |

| DQSL | |

| NDQSL | |

| DQSU | |

| NDQSU | |

Outputs | |

| SDRST | |

| SDCLK | |

| SDNCLK | |

| SDA | [ADDRESS_NUMBER - 1 : 0 ] |

| SDBA | [ 2 : 0 ] |

| SDWE | |

| SDRAS | |

| SDCAS | |

| SDCKE | |

| SDODT | |

| SDDML | |

| SDDMU | |

| mclk | |

| idelay_ctrl_reset | |

| locked_mmcm | |

| locked_pll | |

| dly_ready | |

| dci_ready | |

| phy_locked_mmcm | |

| phy_locked_pll | |

| phy_dly_ready | |

| phy_dci_ready | |

| tmp_debug | [ 7 : 0 ] |

| ps_rdy | |

| ps_out | [PHASE_WIDTH - 1 : 0 ] |

| phy_cmd_nop | |

| phy_cmd_add_pause | |

| pause_len | [CMD_PAUSE_BITS - 1 : 0 ] |

| sequence_done | |

| buf_wdata | [ 63 : 0 ] |

| buf_wr | |

| buf_rd | |

| buf_rst | |

Parameters | |

| ADDRESS_NUMBER | 15 |

| PHASE_WIDTH | 8 |

| SLEW_DQ | "SLOW" |

| SLEW_DQS | "SLOW" |

| SLEW_CMDA | "SLOW" |

| SLEW_CLK | "SLOW" |

| IBUF_LOW_PWR | "TRUE" |

| REFCLK_FREQUENCY | real 300 . 0 |

| HIGH_PERFORMANCE_MODE | "FALSE" |

| CLKIN_PERIOD | 10 |

| CLKFBOUT_MULT | 8 |

| DIVCLK_DIVIDE | 1 |

| CLKFBOUT_USE_FINE_PS | 1 |

| CLKFBOUT_PHASE | 0 . 000 |

| SDCLK_PHASE | 0 . 000 |

| CLK_PHASE | 0 . 000 |

| CLK_DIV_PHASE | 0 . 000 |

| MCLK_PHASE | 90 . 000 |

| REF_JITTER1 | 0 . 010 |

| SS_EN | "FALSE" |

| SS_MODE | "CENTER_HIGH" |

| SS_MOD_PERIOD | 10000 |

| CMD_PAUSE_BITS | 10 |

| CMD_DONE_BIT | 10 |

Module Instances | |

| phy_top::phy_top_i | Module phy_top |

Detailed Description

Member Function Documentation

Member Data Documentation

|

Parameter |

|

Parameter |

|

Parameter |

|

Parameter |

|

Parameter |

|

Parameter |

|

Parameter |

|

Parameter |

|

Parameter |

|

Parameter |

|

Parameter |

|

Parameter |

|

Parameter |

|

Parameter |

|

Parameter |

|

Parameter |

|

Parameter |

|

Output |

|

Output |

|

Output |

|

Output |

|

Output |

|

Output |

|

Output |

|

Output |

|

Output |

|

Input |

|

Output |

|

Output |

|

Output |

|

Output |

|

Input |

|

Input |

|

Input |

|

Input |

|

Input |

|

Input |

|

Input |

|

Signal |

|

Signal |

|

Signal |

|

Signal |

|

Signal |

|

Signal |

|

Signal |

|

Signal |

|

Signal |

|

Signal |

|

Signal |

|

Signal |

|

Signal |

|

Signal |

|

Signal |

|

Signal |

|

Signal |

|

Signal |

|

Signal |

|

Signal |

|

Signal |

|

Signal |

|

Signal |

|

Signal |

|

Signal |

|

Signal |

|

Signal |

|

Signal |

|

Signal |

|

Signal |

|

Signal |

|

Signal |

|

Signal |

|

Signal |

|

Signal |

|

Signal |

|

Signal |

|

Signal |

|

Signal |

|

Signal |

|

Signal |

|

Signal |

|

Signal |

|

Signal |

|

Signal |

|

Signal |

|

Signal |

|

Signal |

|

Signal |

|

Signal |

|

Signal |

|

Signal |

|

Signal |

|

Signal |

|

Signal |

The documentation for this Module was generated from the following files:

- memctrl/phy/phy_cmd.v