Static Public Member Functions |

Always Constructs | |

| ALWAYS_316 | ( mclk ) |

| ALWAYS_317 | ( mclk ) |

| ALWAYS_318 | ( mclk ) |

| ALWAYS_319 | ( mclk ) |

| ALWAYS_320 | ( mclk ) |

Public Attributes |

Inputs | |

| clk_in | |

| rst_in | |

| mrst | |

| ref_clk | |

| cmd0_clk | |

| cmd0_we | |

| cmd0_addr | [ 9 : 0 ] |

| cmd0_data | [ 31 : 0 ] |

| cmd1_clk | |

| cmd1_we | |

| cmd1_addr | [ 9 : 0 ] |

| cmd1_data | [ 31 : 0 ] |

| run_addr | [ 10 : 0 ] |

| run_chn | [ 3 : 0 ] |

| run_refresh | |

| run_seq | |

| cmd_ad | [ 7 : 0 ] |

| cmd_stb | |

| status_start | |

| ext_buf_rdata | [ 63 : 0 ] |

Inouts | |

| SDD | [ 15 : 0 ] |

| DQSL | |

| NDQSL | |

| DQSU | |

| NDQSU | |

Outputs | |

| SDRST | |

| SDCLK | |

| SDNCLK | |

| SDA | [ADDRESS_NUMBER - 1 : 0 ] |

| SDBA | [ 2 : 0 ] |

| SDWE | |

| SDRAS | |

| SDCAS | |

| SDCKE | |

| SDODT | |

| SDDML | |

| SDDMU | |

| mclk | |

| locked | |

| idelay_ctrl_reset | |

| run_done | |

| run_busy | |

| mcontr_reset | |

| status_ad | [ 7 : 0 ] |

| status_rq | |

| ext_buf_page_nxt | |

| ext_buf_rd | |

| ext_buf_rpage_nxt | |

| ext_buf_rchn | [ 3 : 0 ] |

| ext_buf_rrefresh | |

| ext_buf_rrun | |

| ext_buf_wr | |

| ext_buf_wpage_nxt | |

| ext_buf_wchn | [ 3 : 0 ] |

| ext_buf_wrefresh | |

| ext_buf_wrun | |

| ext_buf_wdata | [ 63 : 0 ] |

| tmp_debug | [ 11 : 0 ] |

Module Instances | |

| cmd_deser::cmd_deser_dly_i | Module cmd_deser |

| cmd_deser::cmd_deser_0bit_i | Module cmd_deser |

| cmd_deser::cmd_deser_16bit_i | Module cmd_deser |

| status_generate::status_generate_i | Module status_generate |

| ram_1kx32_1kx32::cmd0_buf_i | Module ram_1kx32_1kx32 |

| ram_1kx32_1kx32::cmd1_buf_i | Module ram_1kx32_1kx32 |

| phy_cmd::phy_cmd_i | Module phy_cmd |

| dly_16::buf_wr_dly_i | Module dly_16 |

| dly_16::buf_wchn_dly_i | Module dly_16 |

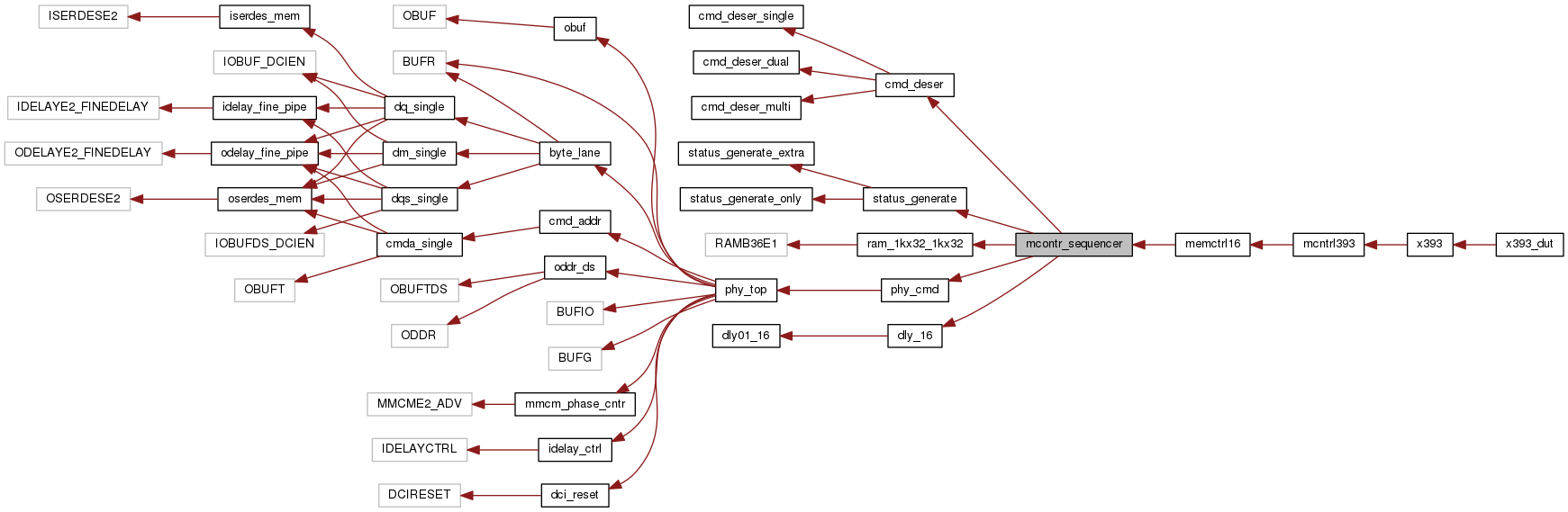

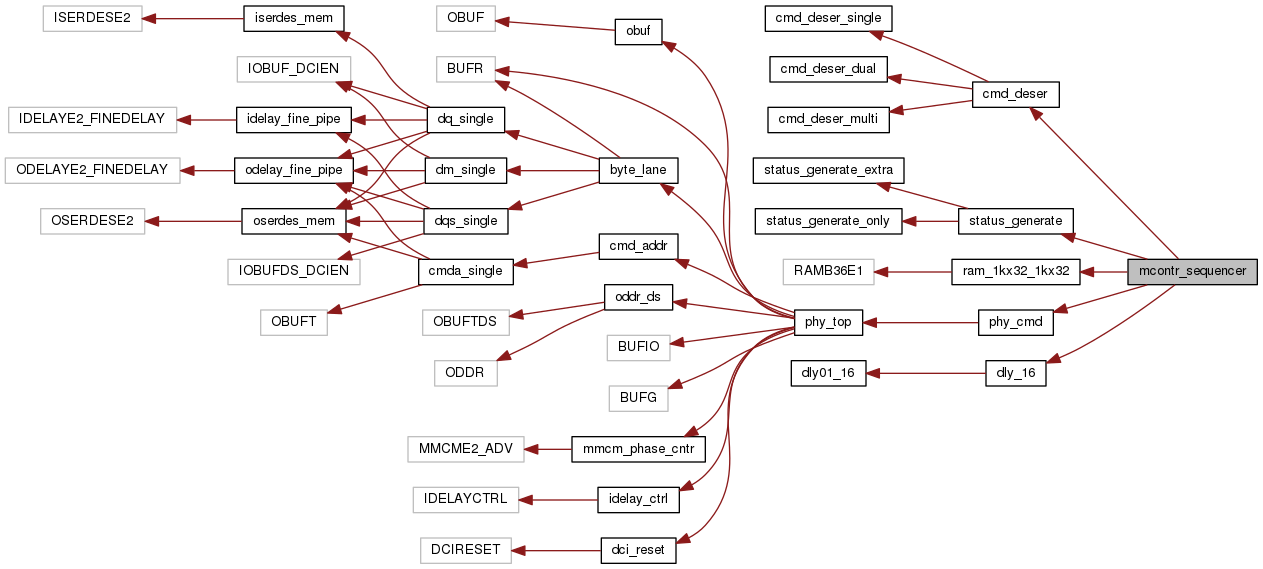

Detailed Description

Definition at line 41 of file mcontr_sequencer.v.

Member Function Documentation

|

Always Construct |

Definition at line 357 of file mcontr_sequencer.v.

|

Always Construct |

Definition at line 406 of file mcontr_sequencer.v.

|

Always Construct |

Definition at line 453 of file mcontr_sequencer.v.

|

Always Construct |

Definition at line 498 of file mcontr_sequencer.v.

|

Always Construct |

Definition at line 505 of file mcontr_sequencer.v.

Member Data Documentation

|

Parameter |

Definition at line 44 of file mcontr_sequencer.v.

|

Parameter |

Definition at line 45 of file mcontr_sequencer.v.

|

Parameter |

Definition at line 51 of file mcontr_sequencer.v.

|

Parameter |

Definition at line 52 of file mcontr_sequencer.v.

|

Parameter |

Definition at line 58 of file mcontr_sequencer.v.

|

Parameter |

Definition at line 60 of file mcontr_sequencer.v.

|

Parameter |

Definition at line 61 of file mcontr_sequencer.v.

|

Parameter |

Definition at line 62 of file mcontr_sequencer.v.

|

Parameter |

Definition at line 63 of file mcontr_sequencer.v.

|

Parameter |

Definition at line 64 of file mcontr_sequencer.v.

|

Parameter |

Definition at line 65 of file mcontr_sequencer.v.

|

Parameter |

Definition at line 71 of file mcontr_sequencer.v.

|

Parameter |

Definition at line 72 of file mcontr_sequencer.v.

|

Parameter |

Definition at line 73 of file mcontr_sequencer.v.

|

Parameter |

Definition at line 74 of file mcontr_sequencer.v.

|

Parameter |

Definition at line 75 of file mcontr_sequencer.v.

|

Parameter |

Definition at line 76 of file mcontr_sequencer.v.

|

Parameter |

Definition at line 77 of file mcontr_sequencer.v.

|

Parameter |

Definition at line 79 of file mcontr_sequencer.v.

|

Parameter |

Definition at line 80 of file mcontr_sequencer.v.

|

Parameter |

Definition at line 81 of file mcontr_sequencer.v.

|

Parameter |

Definition at line 82 of file mcontr_sequencer.v.

|

Parameter |

Definition at line 83 of file mcontr_sequencer.v.

|

Parameter |

Definition at line 84 of file mcontr_sequencer.v.

|

Parameter |

Definition at line 85 of file mcontr_sequencer.v.

|

Parameter |

Definition at line 86 of file mcontr_sequencer.v.

|

Parameter |

Definition at line 88 of file mcontr_sequencer.v.

|

Parameter |

Definition at line 89 of file mcontr_sequencer.v.

|

Parameter |

Definition at line 90 of file mcontr_sequencer.v.

|

Parameter |

Definition at line 91 of file mcontr_sequencer.v.

|

Parameter |

Definition at line 92 of file mcontr_sequencer.v.

|

Parameter |

Definition at line 93 of file mcontr_sequencer.v.

|

Parameter |

Definition at line 94 of file mcontr_sequencer.v.

|

Parameter |

Definition at line 95 of file mcontr_sequencer.v.

|

Parameter |

Definition at line 96 of file mcontr_sequencer.v.

|

Parameter |

Definition at line 97 of file mcontr_sequencer.v.

|

Parameter |

Definition at line 98 of file mcontr_sequencer.v.

|

Parameter |

Definition at line 99 of file mcontr_sequencer.v.

|

Parameter |

Definition at line 100 of file mcontr_sequencer.v.

|

Parameter |

Definition at line 101 of file mcontr_sequencer.v.

|

Parameter |

Definition at line 102 of file mcontr_sequencer.v.

|

Parameter |

Definition at line 103 of file mcontr_sequencer.v.

|

Parameter |

Definition at line 104 of file mcontr_sequencer.v.

|

Parameter |

Definition at line 105 of file mcontr_sequencer.v.

|

Parameter |

Definition at line 106 of file mcontr_sequencer.v.

|

Parameter |

Definition at line 107 of file mcontr_sequencer.v.

|

Parameter |

Definition at line 108 of file mcontr_sequencer.v.

|

Parameter |

Definition at line 109 of file mcontr_sequencer.v.

|

Parameter |

Definition at line 110 of file mcontr_sequencer.v.

|

Output |

Definition at line 113 of file mcontr_sequencer.v.

|

Output |

Definition at line 114 of file mcontr_sequencer.v.

|

Output |

Definition at line 115 of file mcontr_sequencer.v.

|

Output |

Definition at line 116 of file mcontr_sequencer.v.

|

Output |

Definition at line 117 of file mcontr_sequencer.v.

|

Output |

Definition at line 118 of file mcontr_sequencer.v.

|

Output |

Definition at line 119 of file mcontr_sequencer.v.

|

Output |

Definition at line 120 of file mcontr_sequencer.v.

|

Output |

Definition at line 121 of file mcontr_sequencer.v.

|

Output |

Definition at line 122 of file mcontr_sequencer.v.

|

Inout |

Definition at line 124 of file mcontr_sequencer.v.

|

Output |

Definition at line 125 of file mcontr_sequencer.v.

|

Inout |

Definition at line 126 of file mcontr_sequencer.v.

|

Inout |

Definition at line 127 of file mcontr_sequencer.v.

|

Output |

Definition at line 128 of file mcontr_sequencer.v.

|

Inout |

Definition at line 129 of file mcontr_sequencer.v.

|

Inout |

Definition at line 130 of file mcontr_sequencer.v.

|

Input |

Definition at line 132 of file mcontr_sequencer.v.

|

Input |

Definition at line 133 of file mcontr_sequencer.v.

|

Output |

Definition at line 134 of file mcontr_sequencer.v.

|

Input |

Definition at line 135 of file mcontr_sequencer.v.

|

Output |

Definition at line 136 of file mcontr_sequencer.v.

|

Input |

Definition at line 137 of file mcontr_sequencer.v.

|

Output |

Definition at line 138 of file mcontr_sequencer.v.

|

Input |

Definition at line 140 of file mcontr_sequencer.v.

|

Input |

Definition at line 141 of file mcontr_sequencer.v.

|

Input |

Definition at line 142 of file mcontr_sequencer.v.

|

Input |

Definition at line 143 of file mcontr_sequencer.v.

|

Input |

Definition at line 145 of file mcontr_sequencer.v.

|

Input |

Definition at line 146 of file mcontr_sequencer.v.

|

Input |

Definition at line 147 of file mcontr_sequencer.v.

|

Input |

Definition at line 148 of file mcontr_sequencer.v.

|

Input |

Definition at line 150 of file mcontr_sequencer.v.

|

Input |

Definition at line 151 of file mcontr_sequencer.v.

|

Input |

Definition at line 152 of file mcontr_sequencer.v.

|

Input |

Definition at line 153 of file mcontr_sequencer.v.

|

Output |

Definition at line 154 of file mcontr_sequencer.v.

|

Output |

Definition at line 155 of file mcontr_sequencer.v.

|

Output |

Definition at line 156 of file mcontr_sequencer.v.

|

Input |

Definition at line 158 of file mcontr_sequencer.v.

|

Input |

Definition at line 159 of file mcontr_sequencer.v.

|

Output |

Definition at line 160 of file mcontr_sequencer.v.

|

Output |

Definition at line 161 of file mcontr_sequencer.v.

|

Input |

Definition at line 162 of file mcontr_sequencer.v.

|

Output |

Definition at line 167 of file mcontr_sequencer.v.

|

Output |

Definition at line 168 of file mcontr_sequencer.v.

|

Output |

Definition at line 169 of file mcontr_sequencer.v.

|

Output |

Definition at line 171 of file mcontr_sequencer.v.

|

Output |

Definition at line 172 of file mcontr_sequencer.v.

|

Output |

Definition at line 173 of file mcontr_sequencer.v.

|

Input |

Definition at line 174 of file mcontr_sequencer.v.

|

Output |

Definition at line 179 of file mcontr_sequencer.v.

|

Output |

Definition at line 180 of file mcontr_sequencer.v.

|

Output |

Definition at line 182 of file mcontr_sequencer.v.

|

Output |

Definition at line 183 of file mcontr_sequencer.v.

|

Output |

Definition at line 184 of file mcontr_sequencer.v.

|

Output |

Definition at line 185 of file mcontr_sequencer.v.

|

Output |

Definition at line 187 of file mcontr_sequencer.v.

|

Parameter |

Definition at line 189 of file mcontr_sequencer.v.

|

Signal |

Definition at line 190 of file mcontr_sequencer.v.

|

Signal |

Definition at line 191 of file mcontr_sequencer.v.

|

Signal |

Definition at line 192 of file mcontr_sequencer.v.

|

Signal |

Definition at line 193 of file mcontr_sequencer.v.

|

Signal |

Definition at line 194 of file mcontr_sequencer.v.

|

Signal |

Definition at line 195 of file mcontr_sequencer.v.

|

Signal |

Definition at line 196 of file mcontr_sequencer.v.

|

Signal |

Definition at line 197 of file mcontr_sequencer.v.

|

Signal |

Definition at line 198 of file mcontr_sequencer.v.

|

Signal |

Definition at line 199 of file mcontr_sequencer.v.

|

Signal |

Definition at line 200 of file mcontr_sequencer.v.

|

Signal |

Definition at line 202 of file mcontr_sequencer.v.

|

Signal |

Definition at line 203 of file mcontr_sequencer.v.

|

Signal |

Definition at line 204 of file mcontr_sequencer.v.

|

Signal |

Definition at line 205 of file mcontr_sequencer.v.

|

Signal |

Definition at line 206 of file mcontr_sequencer.v.

|

Signal |

Definition at line 207 of file mcontr_sequencer.v.

|

Signal |

Definition at line 208 of file mcontr_sequencer.v.

|

Signal |

Definition at line 209 of file mcontr_sequencer.v.

|

Signal |

Definition at line 211 of file mcontr_sequencer.v.

|

Signal |

Definition at line 212 of file mcontr_sequencer.v.

|

Signal |

Definition at line 213 of file mcontr_sequencer.v.

|

Signal |

Definition at line 215 of file mcontr_sequencer.v.

|

Signal |

Definition at line 219 of file mcontr_sequencer.v.

|

Signal |

Definition at line 220 of file mcontr_sequencer.v.

|

Signal |

Definition at line 221 of file mcontr_sequencer.v.

|

Signal |

Definition at line 222 of file mcontr_sequencer.v.

|

Signal |

Definition at line 226 of file mcontr_sequencer.v.

|

Signal |

Definition at line 227 of file mcontr_sequencer.v.

|

Signal |

Definition at line 229 of file mcontr_sequencer.v.

|

Signal |

Definition at line 232 of file mcontr_sequencer.v.

|

Signal |

Definition at line 233 of file mcontr_sequencer.v.

|

Signal |

Definition at line 234 of file mcontr_sequencer.v.

|

Signal |

Definition at line 235 of file mcontr_sequencer.v.

|

Signal |

Definition at line 239 of file mcontr_sequencer.v.

|

Signal |

Definition at line 240 of file mcontr_sequencer.v.

|

Signal |

Definition at line 241 of file mcontr_sequencer.v.

|

Signal |

Definition at line 242 of file mcontr_sequencer.v.

|

Signal |

Definition at line 243 of file mcontr_sequencer.v.

|

Signal |

Definition at line 244 of file mcontr_sequencer.v.

|

Signal |

Definition at line 245 of file mcontr_sequencer.v.

|

Signal |

Definition at line 246 of file mcontr_sequencer.v.

|

Signal |

Definition at line 247 of file mcontr_sequencer.v.

|

Signal |

Definition at line 248 of file mcontr_sequencer.v.

|

Signal |

Definition at line 249 of file mcontr_sequencer.v.

|

Signal |

Definition at line 250 of file mcontr_sequencer.v.

|

Signal |

Definition at line 251 of file mcontr_sequencer.v.

|

Signal |

Definition at line 252 of file mcontr_sequencer.v.

|

Signal |

Definition at line 253 of file mcontr_sequencer.v.

|

Signal |

Definition at line 254 of file mcontr_sequencer.v.

|

Signal |

Definition at line 255 of file mcontr_sequencer.v.

|

Signal |

Definition at line 256 of file mcontr_sequencer.v.

|

Signal |

Definition at line 257 of file mcontr_sequencer.v.

|

Signal |

Definition at line 258 of file mcontr_sequencer.v.

|

Signal |

Definition at line 259 of file mcontr_sequencer.v.

|

Signal |

Definition at line 260 of file mcontr_sequencer.v.

|

Signal |

Definition at line 261 of file mcontr_sequencer.v.

|

Signal |

Definition at line 262 of file mcontr_sequencer.v.

|

Signal |

Definition at line 263 of file mcontr_sequencer.v.

|

Signal |

Definition at line 264 of file mcontr_sequencer.v.

|

Signal |

Definition at line 266 of file mcontr_sequencer.v.

|

Signal |

Definition at line 267 of file mcontr_sequencer.v.

|

Signal |

Definition at line 268 of file mcontr_sequencer.v.

|

Signal |

Definition at line 270 of file mcontr_sequencer.v.

|

Signal |

Definition at line 271 of file mcontr_sequencer.v.

|

Signal |

Definition at line 273 of file mcontr_sequencer.v.

|

Signal |

Definition at line 274 of file mcontr_sequencer.v.

|

Signal |

Definition at line 275 of file mcontr_sequencer.v.

|

Signal |

Definition at line 277 of file mcontr_sequencer.v.

|

Signal |

Definition at line 278 of file mcontr_sequencer.v.

|

Signal |

Definition at line 280 of file mcontr_sequencer.v.

|

Signal |

Definition at line 391 of file mcontr_sequencer.v.

|

Signal |

Definition at line 392 of file mcontr_sequencer.v.

|

Signal |

Definition at line 393 of file mcontr_sequencer.v.

|

Signal |

Definition at line 394 of file mcontr_sequencer.v.

|

Signal |

Definition at line 396 of file mcontr_sequencer.v.

|

Signal |

Definition at line 397 of file mcontr_sequencer.v.

|

Signal |

Definition at line 517 of file mcontr_sequencer.v.

|

Signal |

Definition at line 518 of file mcontr_sequencer.v.

|

Module Instance |

Definition at line 322 of file mcontr_sequencer.v.

|

Module Instance |

Definition at line 339 of file mcontr_sequencer.v.

|

Module Instance |

Definition at line 375 of file mcontr_sequencer.v.

|

Module Instance |

Definition at line 649 of file mcontr_sequencer.v.

|

Module Instance |

Definition at line 658 of file mcontr_sequencer.v.

|

Module Instance |

Definition at line 556 of file mcontr_sequencer.v.

|

Module Instance |

Definition at line 519 of file mcontr_sequencer.v.

|

Module Instance |

Definition at line 540 of file mcontr_sequencer.v.

|

Module Instance |

Definition at line 437 of file mcontr_sequencer.v.

The documentation for this Module was generated from the following files:

- memctrl/phy/mcontr_sequencer.v