Public Attributes |

Inputs | |

| reset | wire |

| TXDATA | wire [ 63 : 0 ] |

| TXUSRCLK | wire |

| TXUSRCLK2 | wire |

| TX8B10BBYPASS | wire [ 7 : 0 ] |

| TX8B10BEN | wire |

| TXCHARDISPMODE | wire [ 7 : 0 ] |

| TXCHARDISPVAL | wire [ 7 : 0 ] |

| TXCHARISK | wire [ 7 : 0 ] |

| TXPOLARITY | wire |

| TXRATE | wire [ 2 : 0 ] |

| TXCOMINIT | wire |

| TXCOMWAKE | wire |

| TXELECIDLE | wire |

| RXP | wire |

| RXN | wire |

| RXUSRCLK | wire |

| RXUSRCLK2 | wire |

| RXRATE | wire [ 2 : 0 ] |

| RXELECIDLEMODE | wire [ 1 : 0 ] |

| RXPOLARITY | wire |

| RXCOMMADETEN | wire |

| RXPCOMMAALIGNEN | wire |

| RXMCOMMAALIGNEN | wire |

| RX8B10BEN | wire |

| CPLLREFCLKSEL | wire [ 2 : 0 ] |

| GTREFCLK0 | wire |

| GTREFCLK1 | wire |

| GTNORTHREFCLK0 | wire |

| GTNORTHREFCLK1 | wire |

| GTSOUTHREFCLK0 | wire |

| GTSOUTHREFCLK1 | wire |

| GTGREFCLK | wire |

| QPLLCLK | wire |

| QPLLREFCLK | wire |

| RXSYSCLKSEL | wire [ 1 : 0 ] |

| TXSYSCLKSEL | wire [ 1 : 0 ] |

| TXOUTCLKSEL | wire [ 2 : 0 ] |

| RXOUTCLKSEL | wire [ 2 : 0 ] |

| TXDLYBYPASS | wire |

| RXDLYBYPASS | wire |

| CPLLLOCKDETCLK | wire |

| CPLLLOCKEN | wire |

| CPLLPD | wire |

| CPLLRESET | wire |

| GTRSVD | [ 15 : 0 ] |

| PCSRSVDIN | [ 15 : 0 ] |

| PCSRSVDIN2 | [ 4 : 0 ] |

| PMARSVDIN | [ 4 : 0 ] |

| PMARSVDIN2 | [ 4 : 0 ] |

| TSTIN | [ 19 : 0 ] |

Outputs | |

| TXP | wire |

| TXN | wire |

| TXBUFSTATUS | wire [ 1 : 0 ] |

| TXRATEDONE | wire |

| TXCOMFINISH | wire |

| RXDATA | wire [ 63 : 0 ] |

| RXELECIDLE | wire |

| RXCOMINITDET | wire |

| RXCOMWAKEDET | wire |

| RXBYTEISALIGNED | wire |

| RXBYTEREALIGN | wire |

| RXCOMMADET | wire |

| RXCHARISCOMMA | wire [ 7 : 0 ] |

| RXCHARISK | wire [ 7 : 0 ] |

| RXDISPERR | wire [ 7 : 0 ] |

| RXNOTINTABLE | wire [ 7 : 0 ] |

| GTREFCLKMONITOR | wire |

| CPLLFBCLKLOST | wire |

| CPLLLOCK | wire |

| CPLLREFCLKLOST | wire |

| TXOUTCLKPMA | wire |

| TXOUTCLKPCS | wire |

| TXOUTCLK | wire |

| TXOUTCLKFABRIC | wire |

| tx_serial_clk | wire |

| RXOUTCLKPMA | wire |

| RXOUTCLKPCS | wire |

| RXOUTCLK | wire |

| RXOUTCLKFABRIC | wire |

| rx_serial_clk | wire |

| TSTOUT | [ 9 : 0 ] |

Parameters | |

| CPLL_CFG | [ 23 : 0 ] 29 'h00BC07DC |

| CPLL_FBDIV | integer 4 |

| CPLL_FBDIV_45 | integer 5 |

| CPLL_INIT_CFG | [ 23 : 0 ] 24 'h00001E |

| CPLL_LOCK_CFG | [ 15 : 0 ] 16 'h01E8 |

| CPLL_REFCLK_DIV | integer 1 |

| PMA_RSV3 | [ 1 : 0 ] 1 |

| TXOUT_DIV | 2 |

| RXOUT_DIV | 2 |

| TX_INT_DATAWIDTH | integer 0 |

| TX_DATA_WIDTH | integer 20 |

| RX_DATA_WIDTH | integer 20 |

| RX_INT_DATAWIDTH | integer 0 |

| DEC_MCOMMA_DETECT | "TRUE" |

| DEC_PCOMMA_DETECT | "TRUE" |

| ALIGN_MCOMMA_VALUE | [ 9 : 0 ] 10 'b1010000011 |

| ALIGN_MCOMMA_DET | "TRUE" |

| ALIGN_PCOMMA_VALUE | [ 9 : 0 ] 10 'b0101111100 |

| ALIGN_PCOMMA_DET | "TRUE" |

| ALIGN_COMMA_ENABLE | [ 9 : 0 ] 10 'b1111111111 |

| ALIGN_COMMA_DOUBLE | "FALSE" |

| SATA_BURST_SEQ_LEN | [ 3 : 0 ] 4 'b1111 |

| SATA_CPLL_CFG | "VCO_3000MHZ" |

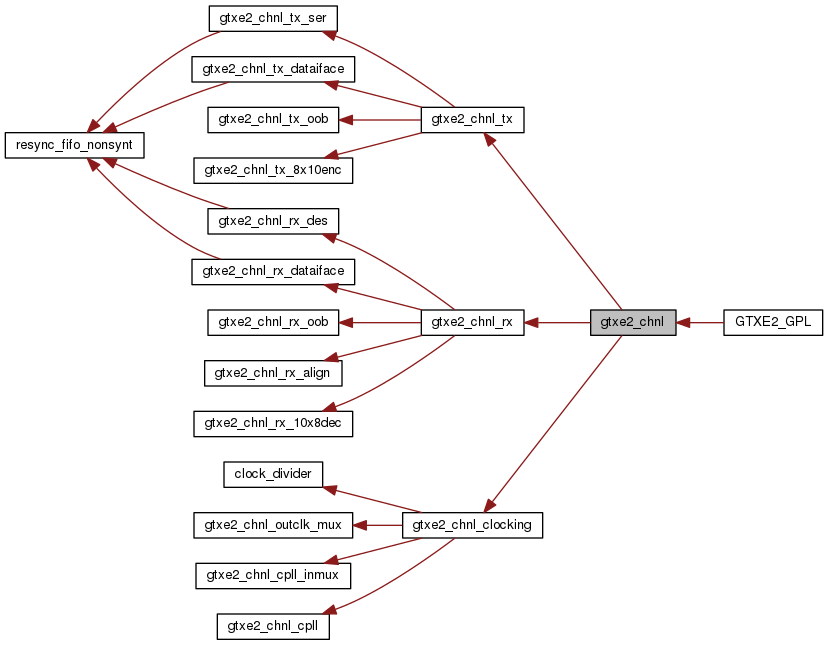

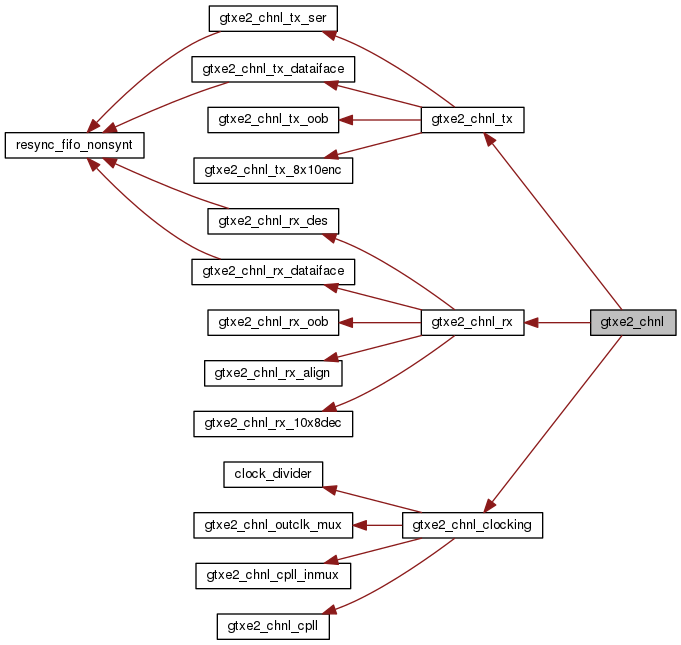

Module Instances | |

| gtxe2_chnl_tx::tx | Module gtxe2_chnl_tx |

| gtxe2_chnl_rx::rx | Module gtxe2_chnl_rx |

| gtxe2_chnl_clocking::clocking | Module gtxe2_chnl_clocking |

Detailed Description

Definition at line 2075 of file GTXE2_GPL.v.

Member Data Documentation

|

Input |

Definition at line 2076 of file GTXE2_GPL.v.

|

Output |

Definition at line 2080 of file GTXE2_GPL.v.

|

Output |

Definition at line 2081 of file GTXE2_GPL.v.

|

Input |

Definition at line 2083 of file GTXE2_GPL.v.

|

Input |

Definition at line 2084 of file GTXE2_GPL.v.

|

Input |

Definition at line 2085 of file GTXE2_GPL.v.

|

Input |

Definition at line 2088 of file GTXE2_GPL.v.

|

Input |

Definition at line 2089 of file GTXE2_GPL.v.

|

Input |

Definition at line 2090 of file GTXE2_GPL.v.

|

Input |

Definition at line 2091 of file GTXE2_GPL.v.

|

Input |

Definition at line 2092 of file GTXE2_GPL.v.

|

Output |

Definition at line 2095 of file GTXE2_GPL.v.

|

Input |

Definition at line 2098 of file GTXE2_GPL.v.

|

Input |

Definition at line 2101 of file GTXE2_GPL.v.

|

Output |

Definition at line 2102 of file GTXE2_GPL.v.

|

Input |

Definition at line 2105 of file GTXE2_GPL.v.

|

Input |

Definition at line 2106 of file GTXE2_GPL.v.

|

Output |

Definition at line 2107 of file GTXE2_GPL.v.

|

Input |

Definition at line 2110 of file GTXE2_GPL.v.

|

Input |

Definition at line 2115 of file GTXE2_GPL.v.

|

Input |

Definition at line 2116 of file GTXE2_GPL.v.

|

Input |

Definition at line 2118 of file GTXE2_GPL.v.

|

Input |

Definition at line 2119 of file GTXE2_GPL.v.

|

Output |

Definition at line 2121 of file GTXE2_GPL.v.

|

Input |

Definition at line 2123 of file GTXE2_GPL.v.

|

Input |

Definition at line 2126 of file GTXE2_GPL.v.

|

Output |

Definition at line 2127 of file GTXE2_GPL.v.

|

Output |

Definition at line 2129 of file GTXE2_GPL.v.

|

Output |

Definition at line 2130 of file GTXE2_GPL.v.

|

Input |

Definition at line 2133 of file GTXE2_GPL.v.

|

Output |

Definition at line 2136 of file GTXE2_GPL.v.

|

Output |

Definition at line 2137 of file GTXE2_GPL.v.

|

Output |

Definition at line 2138 of file GTXE2_GPL.v.

|

Input |

Definition at line 2140 of file GTXE2_GPL.v.

|

Input |

Definition at line 2141 of file GTXE2_GPL.v.

|

Input |

Definition at line 2142 of file GTXE2_GPL.v.

|

Input |

Definition at line 2145 of file GTXE2_GPL.v.

|

Output |

Definition at line 2147 of file GTXE2_GPL.v.

|

Output |

Definition at line 2148 of file GTXE2_GPL.v.

|

Output |

Definition at line 2149 of file GTXE2_GPL.v.

|

Output |

Definition at line 2150 of file GTXE2_GPL.v.

|

Input |

Definition at line 2156 of file GTXE2_GPL.v.

|

Input |

Definition at line 2157 of file GTXE2_GPL.v.

|

Input |

Definition at line 2158 of file GTXE2_GPL.v.

|

Input |

Definition at line 2159 of file GTXE2_GPL.v.

|

Input |

Definition at line 2160 of file GTXE2_GPL.v.

|

Input |

Definition at line 2161 of file GTXE2_GPL.v.

|

Input |

Definition at line 2162 of file GTXE2_GPL.v.

|

Input |

Definition at line 2163 of file GTXE2_GPL.v.

|

Input |

Definition at line 2164 of file GTXE2_GPL.v.

|

Input |

Definition at line 2165 of file GTXE2_GPL.v.

|

Input |

Definition at line 2166 of file GTXE2_GPL.v.

|

Input |

Definition at line 2167 of file GTXE2_GPL.v.

|

Input |

Definition at line 2168 of file GTXE2_GPL.v.

|

Input |

Definition at line 2169 of file GTXE2_GPL.v.

|

Input |

Definition at line 2170 of file GTXE2_GPL.v.

|

Input |

Definition at line 2171 of file GTXE2_GPL.v.

|

Output |

Definition at line 2172 of file GTXE2_GPL.v.

|

Input |

Definition at line 2174 of file GTXE2_GPL.v.

|

Input |

Definition at line 2175 of file GTXE2_GPL.v.

|

Input |

Definition at line 2176 of file GTXE2_GPL.v.

|

Input |

Definition at line 2177 of file GTXE2_GPL.v.

|

Output |

Definition at line 2178 of file GTXE2_GPL.v.

|

Output |

Definition at line 2179 of file GTXE2_GPL.v.

|

Output |

Definition at line 2180 of file GTXE2_GPL.v.

|

Output |

Definition at line 2183 of file GTXE2_GPL.v.

|

Output |

Definition at line 2184 of file GTXE2_GPL.v.

|

Output |

Definition at line 2185 of file GTXE2_GPL.v.

|

Output |

Definition at line 2186 of file GTXE2_GPL.v.

|

Output |

Definition at line 2187 of file GTXE2_GPL.v.

|

Output |

Definition at line 2189 of file GTXE2_GPL.v.

|

Output |

Definition at line 2190 of file GTXE2_GPL.v.

|

Output |

Definition at line 2191 of file GTXE2_GPL.v.

|

Output |

Definition at line 2192 of file GTXE2_GPL.v.

|

Output |

Definition at line 2193 of file GTXE2_GPL.v.

|

Output |

Definition at line 2196 of file GTXE2_GPL.v.

|

Input |

Definition at line 2197 of file GTXE2_GPL.v.

|

Input |

Definition at line 2198 of file GTXE2_GPL.v.

|

Input |

Definition at line 2199 of file GTXE2_GPL.v.

|

Input |

Definition at line 2200 of file GTXE2_GPL.v.

|

Input |

Definition at line 2201 of file GTXE2_GPL.v.

|

Input |

Definition at line 2202 of file GTXE2_GPL.v.

|

Parameter |

Definition at line 2204 of file GTXE2_GPL.v.

|

Parameter |

Definition at line 2205 of file GTXE2_GPL.v.

|

Parameter |

Definition at line 2206 of file GTXE2_GPL.v.

|

Parameter |

Definition at line 2207 of file GTXE2_GPL.v.

|

Parameter |

Definition at line 2208 of file GTXE2_GPL.v.

|

Parameter |

Definition at line 2209 of file GTXE2_GPL.v.

|

Parameter |

Definition at line 2210 of file GTXE2_GPL.v.

|

Parameter |

Definition at line 2212 of file GTXE2_GPL.v.

|

Parameter |

Definition at line 2214 of file GTXE2_GPL.v.

|

Parameter |

Definition at line 2217 of file GTXE2_GPL.v.

|

Parameter |

Definition at line 2218 of file GTXE2_GPL.v.

|

Parameter |

Definition at line 2220 of file GTXE2_GPL.v.

|

Parameter |

Definition at line 2221 of file GTXE2_GPL.v.

|

Parameter |

Definition at line 2223 of file GTXE2_GPL.v.

|

Parameter |

Definition at line 2224 of file GTXE2_GPL.v.

|

Parameter |

Definition at line 2226 of file GTXE2_GPL.v.

|

Parameter |

Definition at line 2227 of file GTXE2_GPL.v.

|

Parameter |

Definition at line 2228 of file GTXE2_GPL.v.

|

Parameter |

Definition at line 2229 of file GTXE2_GPL.v.

|

Parameter |

Definition at line 2230 of file GTXE2_GPL.v.

|

Parameter |

Definition at line 2231 of file GTXE2_GPL.v.

|

Parameter |

Definition at line 2234 of file GTXE2_GPL.v.

|

Parameter |

Definition at line 2235 of file GTXE2_GPL.v.

|

Module Instance |

Definition at line 2323 of file GTXE2_GPL.v.

|

Module Instance |

Definition at line 2274 of file GTXE2_GPL.v.

|

Module Instance |

Definition at line 2237 of file GTXE2_GPL.v.

The documentation for this Module was generated from the following files:

- x393_sata/wrapper/GTXE2_GPL.v