Public Attributes |

Inputs | |

| clk | |

| clk_div | |

| rst | |

| dci_disable | |

| dly_data | [ 7 : 0 ] |

| din | [ 3 : 0 ] |

| tin | [ 3 : 0 ] |

| set_odelay | |

| ld_odelay | |

| set_idelay | |

| ld_idelay | |

Inouts | |

| dqs | |

| ndqs | |

Outputs | |

| dqs_received_dly | |

Parameters | |

| IODELAY_GRP | "IODELAY_MEMORY" |

| IDELAY_VALUE | integer 0 |

| ODELAY_VALUE | integer 0 |

| IBUF_LOW_PWR | "TRUE" |

| IOSTANDARD | "DIFF_SSTL15_T_DCI" |

| SLEW | "SLOW" |

| REFCLK_FREQUENCY | real 300 . 0 |

| HIGH_PERFORMANCE_MODE | "FALSE" |

Signals | |

| wire | d_ser |

| wire | dqs_tri |

| wire | dqs_data_dly |

| wire | dqs_di |

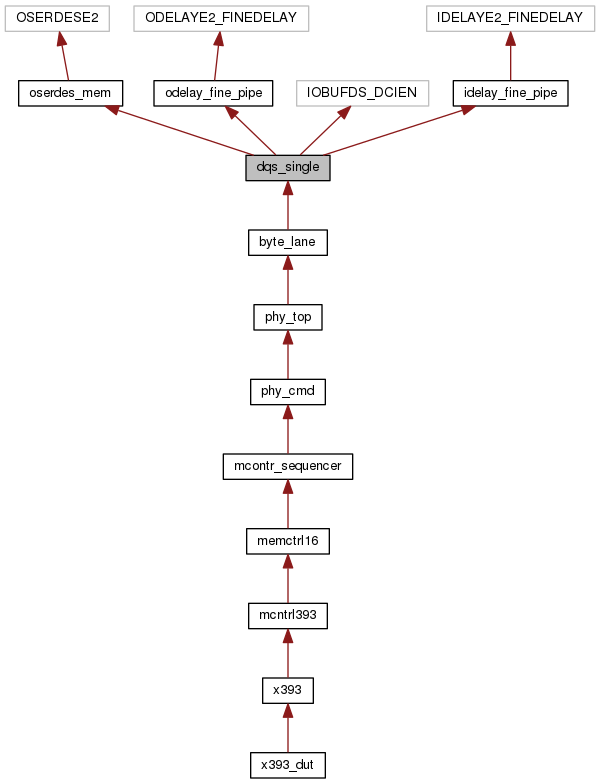

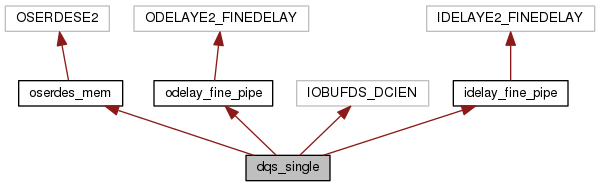

Module Instances | |

| oserdes_mem::oserdes_i | Module oserdes_mem |

| odelay_fine_pipe::dqs_out_dly_i | Module odelay_fine_pipe |

| IOBUFDS_DCIEN::iobufs_dqs_i | Module IOBUFDS_DCIEN |

| idelay_fine_pipe::dqs_in_dly_i | Module idelay_fine_pipe |

Detailed Description

Definition at line 40 of file dqs_single.v.

Member Data Documentation

|

Parameter |

Definition at line 41 of file dqs_single.v.

|

Parameter |

Definition at line 42 of file dqs_single.v.

|

Parameter |

Definition at line 43 of file dqs_single.v.

|

Parameter |

Definition at line 44 of file dqs_single.v.

|

Parameter |

Definition at line 45 of file dqs_single.v.

|

Parameter |

Definition at line 46 of file dqs_single.v.

|

Parameter |

Definition at line 47 of file dqs_single.v.

|

Parameter |

Definition at line 48 of file dqs_single.v.

|

Inout |

Definition at line 50 of file dqs_single.v.

|

Inout |

Definition at line 51 of file dqs_single.v.

|

Input |

Definition at line 52 of file dqs_single.v.

|

Input |

Definition at line 53 of file dqs_single.v.

|

Input |

Definition at line 54 of file dqs_single.v.

|

Output |

Definition at line 55 of file dqs_single.v.

|

Input |

Definition at line 59 of file dqs_single.v.

|

Input |

Definition at line 60 of file dqs_single.v.

|

Input |

Definition at line 61 of file dqs_single.v.

|

Input |

Definition at line 62 of file dqs_single.v.

|

Input |

Definition at line 63 of file dqs_single.v.

|

Input |

Definition at line 64 of file dqs_single.v.

|

Input |

Definition at line 65 of file dqs_single.v.

|

Input |

Definition at line 66 of file dqs_single.v.

|

Signal |

Definition at line 68 of file dqs_single.v.

|

Signal |

Definition at line 69 of file dqs_single.v.

|

Signal |

Definition at line 70 of file dqs_single.v.

|

Signal |

Definition at line 71 of file dqs_single.v.

|

Module Instance |

Definition at line 115 of file dqs_single.v.

|

Module Instance |

Definition at line 100 of file dqs_single.v.

|

Module Instance |

Definition at line 85 of file dqs_single.v.

|

Module Instance |

Definition at line 74 of file dqs_single.v.

The documentation for this Module was generated from the following files:

- memctrl/phy/dqs_single.v