Public Attributes |

Inputs | |

| mclk | |

| dq_tri | [ 1 : 0 ] |

| dqs_tri | [ 1 : 0 ] |

| SDRST | |

| SDCLK | |

| SDNCLK | |

| SDA | [ADDRESS_NUMBER - 1 : 0 ] |

| SDBA | [ 2 : 0 ] |

| SDWE | |

| SDRAS | |

| SDCAS | |

| SDCKE | |

| SDODT | |

| SDDML | |

| SDDMU | |

Inouts | |

| SDD | [ 15 : 0 ] |

| DQSL | |

| NDQSL | |

| DQSU | |

| NDQSU | |

Parameters | |

| ADDRESS_NUMBER | 15 |

| TRISTATE_DELAY_CLK | 4 'h2 |

| TRISTATE_DELAY | 0 |

| CLK_DELAY | 1500 |

| CMDA_DELAY | 1500 |

| DQS_IN_DELAY | 1500 |

| DQ_IN_DELAY | 1500 |

| DQS_OUT_DELAY | 1500 |

| DQ_OUT_DELAY | 1500 |

| CLK_DELAY_H | CLK_DELAY / 4 |

| CMDA_DELAY_H | CMDA_DELAY / 4 |

| DQS_IN_DELAY_H | DQS_IN_DELAY / 4 |

| DQ_IN_DELAY_H | DQ_IN_DELAY / 4 |

| DQS_OUT_DELAY_H | DQS_OUT_DELAY / 4 |

| DQ_OUT_DELAY_H | DQ_OUT_DELAY / 4 |

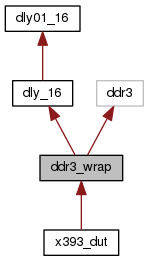

Module Instances | |

| dly_16::dly_16_i | Module dly_16 |

| ddr3::ddr3_i | Module ddr3 |

Detailed Description

Definition at line 42 of file ddr3_wrap.v.

Member Data Documentation

|

Parameter |

Definition at line 43 of file ddr3_wrap.v.

|

Parameter |

Definition at line 44 of file ddr3_wrap.v.

|

Parameter |

Definition at line 45 of file ddr3_wrap.v.

|

Parameter |

Definition at line 46 of file ddr3_wrap.v.

|

Parameter |

Definition at line 47 of file ddr3_wrap.v.

|

Parameter |

Definition at line 48 of file ddr3_wrap.v.

|

Parameter |

Definition at line 49 of file ddr3_wrap.v.

|

Parameter |

Definition at line 50 of file ddr3_wrap.v.

|

Parameter |

Definition at line 51 of file ddr3_wrap.v.

|

Input |

Definition at line 53 of file ddr3_wrap.v.

|

Input |

Definition at line 54 of file ddr3_wrap.v.

|

Input |

Definition at line 55 of file ddr3_wrap.v.

|

Input |

Definition at line 57 of file ddr3_wrap.v.

|

Input |

Definition at line 58 of file ddr3_wrap.v.

|

Input |

Definition at line 59 of file ddr3_wrap.v.

|

Input |

Definition at line 60 of file ddr3_wrap.v.

|

Input |

Definition at line 61 of file ddr3_wrap.v.

|

Input |

Definition at line 62 of file ddr3_wrap.v.

|

Input |

Definition at line 63 of file ddr3_wrap.v.

|

Input |

Definition at line 64 of file ddr3_wrap.v.

|

Input |

Definition at line 65 of file ddr3_wrap.v.

|

Input |

Definition at line 66 of file ddr3_wrap.v.

|

Inout |

Definition at line 68 of file ddr3_wrap.v.

|

Input |

Definition at line 69 of file ddr3_wrap.v.

|

Inout |

Definition at line 70 of file ddr3_wrap.v.

|

Inout |

Definition at line 71 of file ddr3_wrap.v.

|

Input |

Definition at line 72 of file ddr3_wrap.v.

|

Inout |

Definition at line 73 of file ddr3_wrap.v.

|

Inout |

Definition at line 74 of file ddr3_wrap.v.

|

Parameter |

Definition at line 77 of file ddr3_wrap.v.

|

Parameter |

Definition at line 78 of file ddr3_wrap.v.

|

Parameter |

Definition at line 79 of file ddr3_wrap.v.

|

Parameter |

Definition at line 80 of file ddr3_wrap.v.

|

Parameter |

Definition at line 81 of file ddr3_wrap.v.

|

Parameter |

Definition at line 82 of file ddr3_wrap.v.

|

Signal |

Definition at line 84 of file ddr3_wrap.v.

|

Signal |

Definition at line 85 of file ddr3_wrap.v.

|

Signal |

Definition at line 86 of file ddr3_wrap.v.

|

Signal |

Definition at line 87 of file ddr3_wrap.v.

|

Signal |

Definition at line 88 of file ddr3_wrap.v.

|

Signal |

Definition at line 89 of file ddr3_wrap.v.

|

Signal |

Definition at line 90 of file ddr3_wrap.v.

|

Signal |

Definition at line 91 of file ddr3_wrap.v.

|

Signal |

Definition at line 92 of file ddr3_wrap.v.

|

Signal |

Definition at line 93 of file ddr3_wrap.v.

|

Signal |

Definition at line 95 of file ddr3_wrap.v.

|

Signal |

Definition at line 96 of file ddr3_wrap.v.

|

Signal |

Definition at line 97 of file ddr3_wrap.v.

|

Signal |

Definition at line 98 of file ddr3_wrap.v.

|

Signal |

Definition at line 99 of file ddr3_wrap.v.

|

Signal |

Definition at line 100 of file ddr3_wrap.v.

|

Signal |

Definition at line 101 of file ddr3_wrap.v.

|

Signal |

Definition at line 102 of file ddr3_wrap.v.

|

Signal |

Definition at line 103 of file ddr3_wrap.v.

|

Signal |

Definition at line 104 of file ddr3_wrap.v.

|

Signal |

Definition at line 106 of file ddr3_wrap.v.

|

Signal |

Definition at line 107 of file ddr3_wrap.v.

|

Signal |

Definition at line 108 of file ddr3_wrap.v.

|

Signal |

Definition at line 109 of file ddr3_wrap.v.

|

Signal |

Definition at line 110 of file ddr3_wrap.v.

|

Signal |

Definition at line 111 of file ddr3_wrap.v.

|

Signal |

Definition at line 112 of file ddr3_wrap.v.

|

Signal |

Definition at line 113 of file ddr3_wrap.v.

|

Signal |

Definition at line 114 of file ddr3_wrap.v.

|

Signal |

Definition at line 115 of file ddr3_wrap.v.

|

Signal |

Definition at line 117 of file ddr3_wrap.v.

|

Signal |

Definition at line 118 of file ddr3_wrap.v.

|

Signal |

Definition at line 119 of file ddr3_wrap.v.

|

Signal |

Definition at line 120 of file ddr3_wrap.v.

|

Signal |

Definition at line 121 of file ddr3_wrap.v.

|

Signal |

Definition at line 122 of file ddr3_wrap.v.

|

Signal |

Definition at line 123 of file ddr3_wrap.v.

|

Signal |

Definition at line 124 of file ddr3_wrap.v.

|

Signal |

Definition at line 125 of file ddr3_wrap.v.

|

Signal |

Definition at line 126 of file ddr3_wrap.v.

|

Signal |

Definition at line 128 of file ddr3_wrap.v.

|

Signal |

Definition at line 129 of file ddr3_wrap.v.

|

Signal |

Definition at line 130 of file ddr3_wrap.v.

|

Signal |

Definition at line 131 of file ddr3_wrap.v.

|

Signal |

Definition at line 133 of file ddr3_wrap.v.

|

Signal |

Definition at line 134 of file ddr3_wrap.v.

|

Signal |

Definition at line 135 of file ddr3_wrap.v.

|

Signal |

Definition at line 136 of file ddr3_wrap.v.

|

Signal |

Definition at line 137 of file ddr3_wrap.v.

|

Signal |

Definition at line 138 of file ddr3_wrap.v.

|

Signal |

Definition at line 139 of file ddr3_wrap.v.

|

Signal |

Definition at line 140 of file ddr3_wrap.v.

|

Signal |

Definition at line 141 of file ddr3_wrap.v.

|

Signal |

Definition at line 142 of file ddr3_wrap.v.

|

Signal |

Definition at line 143 of file ddr3_wrap.v.

|

Signal |

Definition at line 144 of file ddr3_wrap.v.

|

Signal |

Definition at line 145 of file ddr3_wrap.v.

|

Signal |

Definition at line 146 of file ddr3_wrap.v.

|

Signal |

Definition at line 150 of file ddr3_wrap.v.

|

Signal |

Definition at line 151 of file ddr3_wrap.v.

|

Signal |

Definition at line 156 of file ddr3_wrap.v.

|

Signal |

Definition at line 157 of file ddr3_wrap.v.

|

Signal |

Definition at line 170 of file ddr3_wrap.v.

|

Signal |

Definition at line 171 of file ddr3_wrap.v.

|

Signal |

Definition at line 172 of file ddr3_wrap.v.

|

Signal |

Definition at line 173 of file ddr3_wrap.v.

|

Signal |

Definition at line 174 of file ddr3_wrap.v.

|

Signal |

Definition at line 175 of file ddr3_wrap.v.

|

Signal |

Definition at line 176 of file ddr3_wrap.v.

|

Signal |

Definition at line 178 of file ddr3_wrap.v.

|

Signal |

Definition at line 179 of file ddr3_wrap.v.

|

Signal |

Definition at line 180 of file ddr3_wrap.v.

|

Signal |

Definition at line 181 of file ddr3_wrap.v.

|

Signal |

Definition at line 182 of file ddr3_wrap.v.

|

Signal |

Definition at line 183 of file ddr3_wrap.v.

|

Signal |

Definition at line 184 of file ddr3_wrap.v.

|

Signal |

Definition at line 186 of file ddr3_wrap.v.

|

Signal |

Definition at line 187 of file ddr3_wrap.v.

|

Signal |

Definition at line 188 of file ddr3_wrap.v.

|

Signal |

Definition at line 189 of file ddr3_wrap.v.

|

Signal |

Definition at line 190 of file ddr3_wrap.v.

|

Signal |

Definition at line 191 of file ddr3_wrap.v.

|

Signal |

Definition at line 192 of file ddr3_wrap.v.

|

Signal |

Definition at line 194 of file ddr3_wrap.v.

|

Signal |

Definition at line 195 of file ddr3_wrap.v.

|

Signal |

Definition at line 196 of file ddr3_wrap.v.

|

Signal |

Definition at line 197 of file ddr3_wrap.v.

|

Signal |

Definition at line 198 of file ddr3_wrap.v.

|

Signal |

Definition at line 199 of file ddr3_wrap.v.

|

Signal |

Definition at line 200 of file ddr3_wrap.v.

|

Signal |

Definition at line 202 of file ddr3_wrap.v.

|

Signal |

Definition at line 203 of file ddr3_wrap.v.

|

Signal |

Definition at line 204 of file ddr3_wrap.v.

|

Signal |

Definition at line 205 of file ddr3_wrap.v.

|

Signal |

Definition at line 206 of file ddr3_wrap.v.

|

Signal |

Definition at line 208 of file ddr3_wrap.v.

|

Signal |

Definition at line 209 of file ddr3_wrap.v.

|

Signal |

Definition at line 210 of file ddr3_wrap.v.

|

Signal |

Definition at line 211 of file ddr3_wrap.v.

|

Signal |

Definition at line 212 of file ddr3_wrap.v.

|

Signal |

Definition at line 214 of file ddr3_wrap.v.

|

Signal |

Definition at line 215 of file ddr3_wrap.v.

|

Signal |

Definition at line 216 of file ddr3_wrap.v.

|

Signal |

Definition at line 217 of file ddr3_wrap.v.

|

Signal |

Definition at line 218 of file ddr3_wrap.v.

|

Module Instance |

Definition at line 297 of file ddr3_wrap.v.

|

Module Instance |

Definition at line 161 of file ddr3_wrap.v.

The documentation for this Module was generated from the following files:

- wrap/ddr3_wrap.v