Static Public Member Functions |

Always Constructs | |

| ALWAYS_201 | ( clk ) |

Public Attributes |

Inputs | |

| clk | |

| rst | |

| din | [WIDTH - 1 : 0 ] |

| pre2_start | |

Outputs | |

| dout_10_32_76_54 | [ 2 *WIDTH - 1 : 0 ] |

| start_out | reg |

| en_out | reg |

Parameters | |

| WIDTH | 24 |

Signals | |

| reg[ 6 : 0 ] | wcntr |

| wire[ 2 : 0 ] | wrow |

| wire[ 2 : 0 ] | wcol |

| wire | wpage |

| reg | wcol13 |

| wire[ 3 : 0 ] | wrow_mod |

| wire[ 1 : 0 ] | wcol01_mod |

| reg[ 6 : 0 ] | waddr |

| wire | pre2_stop |

| reg[WIDTH - 1 : 0 ] | transpose_ram [ 0 : 127 ] |

| reg | pre_we_r |

| reg | we_r |

| reg[ 5 : 0 ] | rcntr |

| reg[ 5 : 0 ] | raddr |

| reg | re_r |

| reg | regen_r |

| reg[ 2 *WIDTH - 1 : 0 ] | ram_reg |

| reg[ 2 *WIDTH - 1 : 0 ] | ram_reg2 |

| wire | pre_rstart_w |

| reg[ 1 : 0 ] | rstop_r |

| reg | first_after_pause |

Module Instances | |

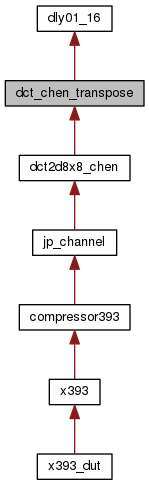

| dly01_16::dly01_16_stop_i | Module dly01_16 |

Detailed Description

Definition at line 41 of file dct_chen_transpose.v.

Member Function Documentation

|

Always Construct |

Definition at line 79 of file dct_chen_transpose.v.

Member Data Documentation

|

Parameter |

Definition at line 42 of file dct_chen_transpose.v.

|

Input |

Definition at line 44 of file dct_chen_transpose.v.

|

Input |

Definition at line 45 of file dct_chen_transpose.v.

Definition at line 46 of file dct_chen_transpose.v.

|

Input |

Definition at line 47 of file dct_chen_transpose.v.

|

Output |

Definition at line 48 of file dct_chen_transpose.v.

|

Output |

Definition at line 49 of file dct_chen_transpose.v.

|

Output |

Definition at line 50 of file dct_chen_transpose.v.

|

Signal |

Definition at line 52 of file dct_chen_transpose.v.

|

Signal |

Definition at line 53 of file dct_chen_transpose.v.

|

Signal |

Definition at line 54 of file dct_chen_transpose.v.

|

Signal |

Definition at line 55 of file dct_chen_transpose.v.

|

Signal |

Definition at line 57 of file dct_chen_transpose.v.

|

Signal |

Definition at line 58 of file dct_chen_transpose.v.

|

Signal |

Definition at line 59 of file dct_chen_transpose.v.

|

Signal |

Definition at line 60 of file dct_chen_transpose.v.

|

Signal |

Definition at line 61 of file dct_chen_transpose.v.

|

Signal |

Definition at line 62 of file dct_chen_transpose.v.

|

Signal |

Definition at line 63 of file dct_chen_transpose.v.

|

Signal |

Definition at line 64 of file dct_chen_transpose.v.

|

Signal |

Definition at line 65 of file dct_chen_transpose.v.

|

Signal |

Definition at line 66 of file dct_chen_transpose.v.

|

Signal |

Definition at line 67 of file dct_chen_transpose.v.

|

Signal |

Definition at line 68 of file dct_chen_transpose.v.

|

Signal |

Definition at line 69 of file dct_chen_transpose.v.

|

Signal |

Definition at line 70 of file dct_chen_transpose.v.

|

Signal |

Definition at line 71 of file dct_chen_transpose.v.

|

Signal |

Definition at line 72 of file dct_chen_transpose.v.

|

Signal |

Definition at line 73 of file dct_chen_transpose.v.

|

Module Instance |

Definition at line 129 of file dct_chen_transpose.v.

The documentation for this Module was generated from the following files: