Static Public Member Functions |

Always Constructs | |

| ALWAYS_466 | ( mclk ) |

| ALWAYS_467 | ( memclk or memclk_rst ) |

| ALWAYS_468 | ( ffclk0 or ffclk0_rst ) |

| ALWAYS_469 | ( ffclk1 or ffclk1_rst ) |

| ALWAYS_470 | ( mclk ) |

Public Attributes |

Inputs | |

| async_rst | |

| mclk | |

| mrst | |

| cmd_ad | [ 7 : 0 ] |

| cmd_stb | |

| status_start | |

| fclk | [ 3 : 0 ] |

| memclk_pad | |

| ffclk0p_pad | |

| ffclk0n_pad | |

| ffclk1p_pad | |

| ffclk1n_pad | |

| extra_status | [ 1 : 0 ] |

Outputs | |

| status_ad | [ 7 : 0 ] |

| status_rq | |

| aclk | |

| hclk | |

| pclk | |

| xclk | |

| sync_clk | |

| time_ref | |

| locked_sync_clk | |

| locked_xclk | |

| locked_pclk | |

| locked_hclk | |

Parameters | |

| CLK_ADDR | 'h728 |

| CLK_MASK | 'h7fe |

| CLK_STATUS_REG_ADDR | 'h3a |

| CLK_CNTRL | 0 |

| CLK_STATUS | 1 |

| CLK_RESET | 'h0 |

| CLK_PWDWN | 'h0 |

| CLKIN_PERIOD_AXIHP | 20 |

| DIVCLK_DIVIDE_AXIHP | 1 |

| CLKFBOUT_MULT_AXIHP | 18 |

| CLKOUT_DIV_AXIHP | 6 |

| BUF_CLK1X_AXIHP | "BUFG " |

| CLKIN_PERIOD_PCLK | 42 |

| DIVCLK_DIVIDE_PCLK | 1 |

| CLKFBOUT_MULT_PCLK | 40 |

| CLKOUT_DIV_PCLK | 10 |

| BUF_CLK1X_PCLK | "BUFG " |

| CLKIN_PERIOD_XCLK | 20 |

| DIVCLK_DIVIDE_XCLK | 1 |

| CLKFBOUT_MULT_XCLK | 20 |

| CLKOUT_DIV_XCLK | 10 |

| BUF_CLK1X_XCLK | "BUFG " |

| CLKIN_PERIOD_SYNC | 20 |

| DIVCLK_DIVIDE_SYNC | 1 |

| CLKFBOUT_MULT_SYNC | 20 |

| CLKOUT_DIV_SYNC | 10 |

| BUF_CLK1X_SYNC | "BUFG " |

| MEMCLK_CAPACITANCE | "DONT_CARE" |

| MEMCLK_IBUF_LOW_PWR | "TRUE" |

| MEMCLK_IOSTANDARD | "DEFAULT" |

| FFCLK0_CAPACITANCE | "DONT_CARE" |

| FFCLK0_DIFF_TERM | "FALSE" |

| FFCLK0_IBUF_LOW_PWR | "TRUE" |

| FFCLK0_IOSTANDARD | "DEFAULT" |

| FFCLK1_CAPACITANCE | "DONT_CARE" |

| FFCLK1_DIFF_TERM | "FALSE" |

| FFCLK1_IBUF_LOW_PWR | "TRUE" |

| FFCLK1_IOSTANDARD | "DEFAULT" |

Signals | |

| wire | memclk |

| wire | ffclk0 |

| wire | ffclk1 |

| wire[ 8 : 0 ] | status_data |

| wire[ 10 : 0 ] | cmd_data |

| wire | cmd_we |

| wire[ 0 : 0 ] | cmd_a |

| wire | set_ctrl_w |

| wire | set_status_w |

| wire[ 3 : 0 ] | locked |

| reg[ 6 : 0 ] | reset_clk |

| reg[ 3 : 0 ] | pwrdwn_clk |

| reg[ 2 : 0 ] | test_clk |

| wire | memclk_rst |

| wire | ffclk0_rst |

| wire | ffclk1_rst |

| reg[ 2 : 0 ] | time_ref_r |

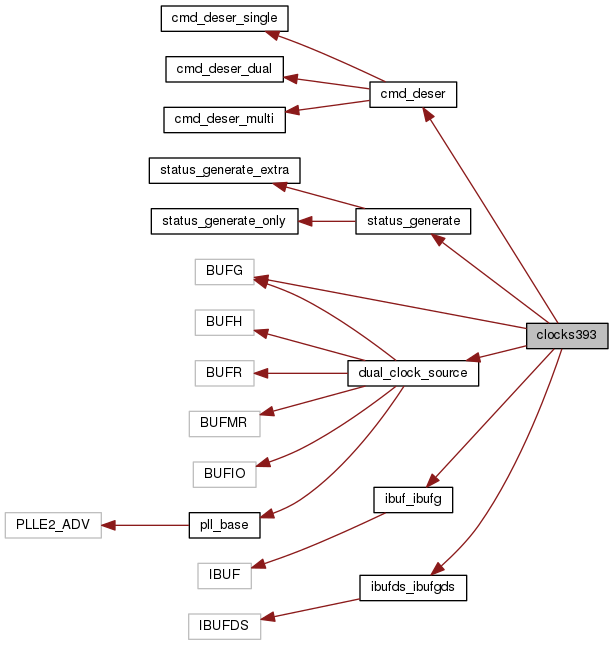

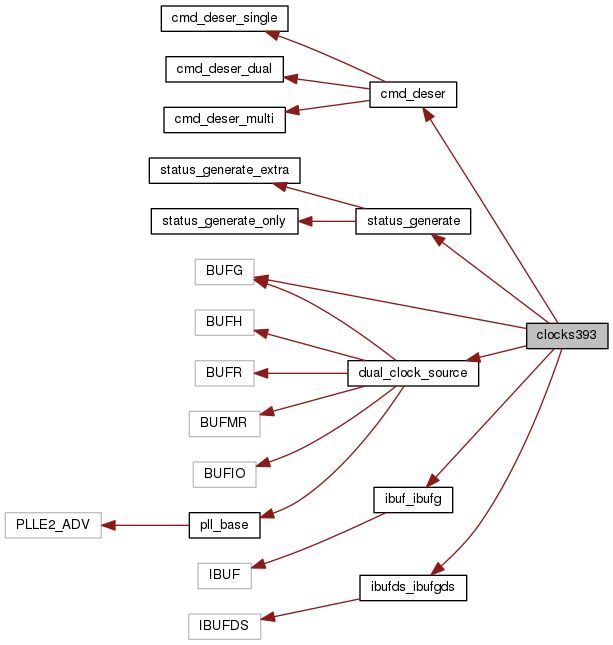

Detailed Description

Definition at line 41 of file clocks393.v.

Member Function Documentation

|

Always Construct |

Definition at line 150 of file clocks393.v.

|

Always Construct |

Definition at line 158 of file clocks393.v.

|

Always Construct |

Definition at line 159 of file clocks393.v.

|

Always Construct |

Definition at line 160 of file clocks393.v.

|

Always Construct |

Definition at line 308 of file clocks393.v.

Member Data Documentation

|

Parameter |

Definition at line 42 of file clocks393.v.

|

Parameter |

Definition at line 43 of file clocks393.v.

|

Parameter |

Definition at line 44 of file clocks393.v.

|

Parameter |

Definition at line 45 of file clocks393.v.

|

Parameter |

Definition at line 46 of file clocks393.v.

|

Parameter |

Definition at line 48 of file clocks393.v.

|

Parameter |

Definition at line 49 of file clocks393.v.

|

Parameter |

Definition at line 51 of file clocks393.v.

|

Parameter |

Definition at line 52 of file clocks393.v.

|

Parameter |

Definition at line 53 of file clocks393.v.

|

Parameter |

Definition at line 54 of file clocks393.v.

|

Parameter |

Definition at line 55 of file clocks393.v.

|

Parameter |

Definition at line 57 of file clocks393.v.

|

Parameter |

Definition at line 58 of file clocks393.v.

|

Parameter |

Definition at line 59 of file clocks393.v.

|

Parameter |

Definition at line 60 of file clocks393.v.

|

Parameter |

Definition at line 61 of file clocks393.v.

|

Parameter |

Definition at line 66 of file clocks393.v.

|

Parameter |

Definition at line 67 of file clocks393.v.

|

Parameter |

Definition at line 68 of file clocks393.v.

|

Parameter |

Definition at line 69 of file clocks393.v.

|

Parameter |

Definition at line 70 of file clocks393.v.

|

Parameter |

Definition at line 75 of file clocks393.v.

|

Parameter |

Definition at line 76 of file clocks393.v.

|

Parameter |

Definition at line 77 of file clocks393.v.

|

Parameter |

Definition at line 78 of file clocks393.v.

|

Parameter |

Definition at line 79 of file clocks393.v.

|

Parameter |

Definition at line 81 of file clocks393.v.

|

Parameter |

Definition at line 82 of file clocks393.v.

|

Parameter |

Definition at line 83 of file clocks393.v.

|

Parameter |

Definition at line 85 of file clocks393.v.

|

Parameter |

Definition at line 86 of file clocks393.v.

|

Parameter |

Definition at line 87 of file clocks393.v.

|

Parameter |

Definition at line 88 of file clocks393.v.

|

Parameter |

Definition at line 90 of file clocks393.v.

|

Parameter |

Definition at line 91 of file clocks393.v.

|

Parameter |

Definition at line 92 of file clocks393.v.

|

Parameter |

Definition at line 93 of file clocks393.v.

|

Input |

Definition at line 96 of file clocks393.v.

|

Input |

Definition at line 97 of file clocks393.v.

|

Input |

Definition at line 98 of file clocks393.v.

|

Input |

Definition at line 100 of file clocks393.v.

|

Input |

Definition at line 101 of file clocks393.v.

|

Output |

Definition at line 102 of file clocks393.v.

|

Output |

Definition at line 103 of file clocks393.v.

|

Input |

Definition at line 104 of file clocks393.v.

|

Input |

Definition at line 105 of file clocks393.v.

|

Input |

Definition at line 106 of file clocks393.v.

|

Input |

Definition at line 107 of file clocks393.v.

|

Input |

Definition at line 108 of file clocks393.v.

|

Input |

Definition at line 109 of file clocks393.v.

|

Input |

Definition at line 110 of file clocks393.v.

|

Output |

Definition at line 111 of file clocks393.v.

|

Output |

Definition at line 112 of file clocks393.v.

|

Output |

Definition at line 113 of file clocks393.v.

|

Output |

Definition at line 116 of file clocks393.v.

|

Output |

Definition at line 119 of file clocks393.v.

|

Output |

Definition at line 120 of file clocks393.v.

|

Input |

Definition at line 121 of file clocks393.v.

|

Output |

Definition at line 122 of file clocks393.v.

|

Output |

Definition at line 123 of file clocks393.v.

|

Output |

Definition at line 124 of file clocks393.v.

|

Output |

Definition at line 125 of file clocks393.v.

|

Signal |

Definition at line 127 of file clocks393.v.

|

Signal |

Definition at line 128 of file clocks393.v.

|

Signal |

Definition at line 129 of file clocks393.v.

|

Signal |

Definition at line 130 of file clocks393.v.

|

Signal |

Definition at line 131 of file clocks393.v.

|

Signal |

Definition at line 132 of file clocks393.v.

|

Signal |

Definition at line 133 of file clocks393.v.

|

Signal |

Definition at line 135 of file clocks393.v.

|

Signal |

Definition at line 136 of file clocks393.v.

|

Signal |

Definition at line 137 of file clocks393.v.

|

Signal |

Definition at line 138 of file clocks393.v.

|

Signal |

Definition at line 139 of file clocks393.v.

|

Signal |

Definition at line 140 of file clocks393.v.

|

Signal |

Definition at line 141 of file clocks393.v.

|

Signal |

Definition at line 142 of file clocks393.v.

|

Signal |

Definition at line 143 of file clocks393.v.

|

Signal |

Definition at line 307 of file clocks393.v.

|

Module Instance |

Definition at line 195 of file clocks393.v.

|

Module Instance |

Definition at line 162 of file clocks393.v.

|

Module Instance |

Definition at line 197 of file clocks393.v.

|

Module Instance |

Definition at line 213 of file clocks393.v.

|

Module Instance |

Definition at line 235 of file clocks393.v.

|

Module Instance |

Definition at line 257 of file clocks393.v.

|

Module Instance |

Definition at line 274 of file clocks393.v.

|

Module Instance |

Definition at line 283 of file clocks393.v.

|

Module Instance |

Definition at line 294 of file clocks393.v.

|

Module Instance |

Definition at line 179 of file clocks393.v.

The documentation for this Module was generated from the following files:

- util_modules/clocks393.v