Static Public Member Functions |

Always Constructs | |

| ALWAYS_588 | ( clk ) |

| ALWAYS_589 | ( datascope_clk ) |

| ALWAYS_590 | ( clk ) |

Public Attributes |

Inputs | |

| exrst | |

| reliable_clk | |

| h2d_data | [ 31 : 0 ] |

| h2d_mask | [ 1 : 0 ] |

| h2d_type | [ 1 : 0 ] |

| h2d_valid | |

| d2h_ready | |

| pcmd_st_cleared | |

| syncesc_send | |

| comreset_send | |

| set_offline | |

| send_R_OK | |

| send_R_ERR | |

| sctl_ipm | [ 3 : 0 ] |

| sctl_spd | [ 3 : 0 ] |

| extclk_p | wire |

| extclk_n | wire |

| rxp_in | wire |

| rxn_in | wire |

| drp_rst | |

| drp_clk | |

| drp_en | |

| drp_we | |

| drp_addr | [ 14 : 0 ] |

| drp_di | [ 15 : 0 ] |

| hclk | |

Outputs | |

| rst | |

| clk | |

| h2d_ready | |

| d2h_data | [ 31 : 0 ] |

| d2h_mask | [ 1 : 0 ] |

| d2h_type | [ 1 : 0 ] |

| d2h_valid | |

| d2h_many | |

| phy_speed | [ 1 : 0 ] |

| gtx_ready | |

| xmit_ok | |

| xmit_err | |

| x_rdy_collision | |

| syncesc_recv | |

| syncesc_send_done | |

| cominit_got | |

| serr_DT | |

| serr_DS | |

| serr_DH | |

| serr_DC | |

| serr_DB | |

| serr_DW | |

| serr_DI | |

| serr_EE | |

| serr_EP | |

| serr_EC | |

| serr_ET | |

| serr_EM | |

| serr_EI | |

| txp_out | wire |

| txn_out | wire |

| datascope_clk | |

| datascope_waddr | [ADDRESS_BITS - 1 : 0 ] |

| datascope_we | |

| datascope_di | [ 31 : 0 ] |

| drp_rdy | |

| drp_do | [ 15 : 0 ] |

| xclk_period | [FREQ_METER_WIDTH - 1 : 0 ] |

| debug_phy | [ 31 : 0 ] |

| debug_link | [ 31 : 0 ] |

Parameters | |

| ADDRESS_BITS | 10 |

| DATASCOPE_START_BIT | 14 |

| DATASCOPE_POST_MEAS | 16 |

| BITS_TO_START_XMIT | 6 |

| DATA_BYTE_WIDTH | 4 |

| ELASTIC_DEPTH | 4 |

| ELASTIC_OFFSET | 7 |

| FREQ_METER_WIDTH | 12 |

| PHY_SPEED | 2 |

| FIFO_ADDR_WIDTH | 9 |

| D2H_TYPE_DMA | 0 |

| D2H_TYPE_FIS_HEAD | 1 |

| D2H_TYPE_OK | 2 |

| D2H_TYPE_ERR | 3 |

| H2D_TYPE_FIS_DATA | 0 |

| H2D_TYPE_FIS_HEAD | 1 |

| H2D_TYPE_FIS_LAST | 2 |

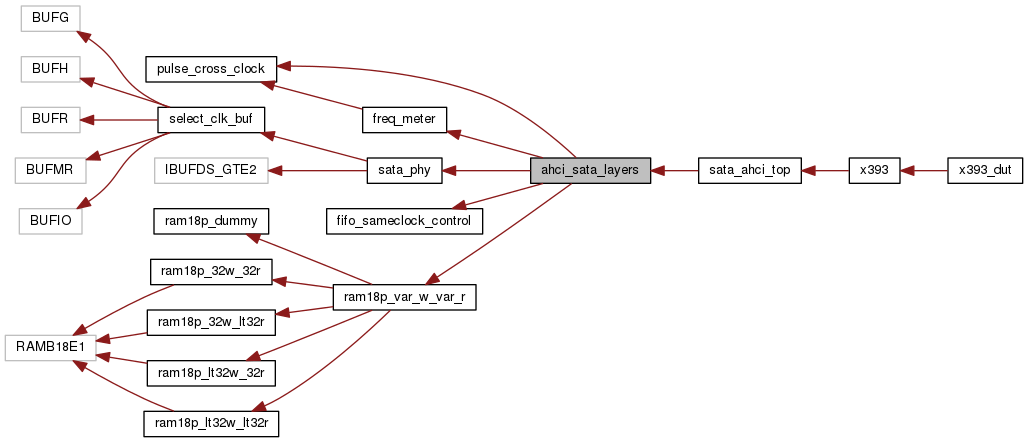

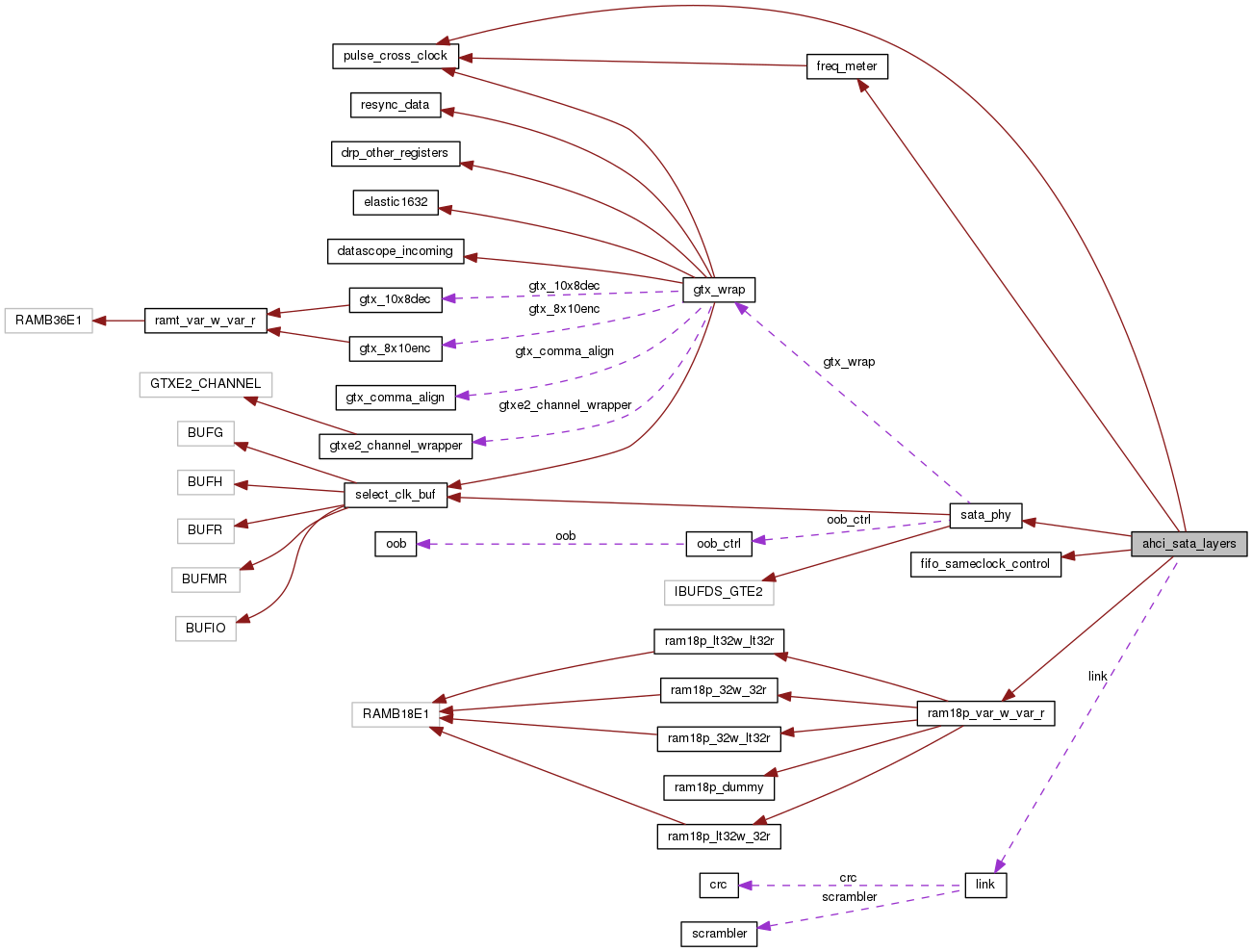

Module Instances | |

| pulse_cross_clock::dbg_was_link5_i | Module pulse_cross_clock |

| link::link | Module link |

| sata_phy::phy | Module sata_phy |

| fifo_sameclock_control::fifo_h2d_control_i | Module fifo_sameclock_control |

| ram18p_var_w_var_r::fifo_h2d_i | Module ram18p_var_w_var_r |

| fifo_sameclock_control::fifo_d2h_control_i | Module fifo_sameclock_control |

| ram18p_var_w_var_r::fifo_d2h_i | Module ram18p_var_w_var_r |

| freq_meter::freq_meter_i | Module freq_meter |

Detailed Description

Definition at line 28 of file ahci_sata_layers.v.

Member Function Documentation

|

Always Construct |

Definition at line 241 of file ahci_sata_layers.v.

|

Always Construct |

Definition at line 253 of file ahci_sata_layers.v.

|

Always Construct |

Definition at line 322 of file ahci_sata_layers.v.

Member Data Documentation

|

Parameter |

Definition at line 30 of file ahci_sata_layers.v.

|

Parameter |

Definition at line 31 of file ahci_sata_layers.v.

|

Parameter |

Definition at line 32 of file ahci_sata_layers.v.

|

Parameter |

Definition at line 34 of file ahci_sata_layers.v.

|

Parameter |

Definition at line 35 of file ahci_sata_layers.v.

|

Parameter |

Definition at line 36 of file ahci_sata_layers.v.

|

Parameter |

Definition at line 37 of file ahci_sata_layers.v.

|

Parameter |

Definition at line 38 of file ahci_sata_layers.v.

|

Input |

Definition at line 41 of file ahci_sata_layers.v.

|

Input |

Definition at line 42 of file ahci_sata_layers.v.

|

Output |

Definition at line 43 of file ahci_sata_layers.v.

|

Output |

Definition at line 44 of file ahci_sata_layers.v.

|

Input |

Definition at line 47 of file ahci_sata_layers.v.

|

Input |

Definition at line 48 of file ahci_sata_layers.v.

|

Input |

Definition at line 49 of file ahci_sata_layers.v.

|

Input |

Definition at line 50 of file ahci_sata_layers.v.

|

Output |

Definition at line 51 of file ahci_sata_layers.v.

|

Output |

Definition at line 54 of file ahci_sata_layers.v.

|

Output |

Definition at line 55 of file ahci_sata_layers.v.

|

Output |

Definition at line 56 of file ahci_sata_layers.v.

|

Output |

Definition at line 57 of file ahci_sata_layers.v.

|

Output |

Definition at line 58 of file ahci_sata_layers.v.

|

Input |

Definition at line 59 of file ahci_sata_layers.v.

|

Output |

Definition at line 62 of file ahci_sata_layers.v.

|

Output |

Definition at line 63 of file ahci_sata_layers.v.

|

Output |

Definition at line 64 of file ahci_sata_layers.v.

|

Output |

Definition at line 65 of file ahci_sata_layers.v.

|

Output |

Definition at line 66 of file ahci_sata_layers.v.

|

Output |

Definition at line 67 of file ahci_sata_layers.v.

|

Input |

Definition at line 69 of file ahci_sata_layers.v.

|

Input |

Definition at line 70 of file ahci_sata_layers.v.

|

Output |

Definition at line 71 of file ahci_sata_layers.v.

|

Input |

Definition at line 72 of file ahci_sata_layers.v.

|

Output |

Definition at line 73 of file ahci_sata_layers.v.

|

Input |

Definition at line 74 of file ahci_sata_layers.v.

|

Input |

Definition at line 76 of file ahci_sata_layers.v.

|

Input |

Definition at line 77 of file ahci_sata_layers.v.

|

Output |

Definition at line 81 of file ahci_sata_layers.v.

|

Output |

Definition at line 82 of file ahci_sata_layers.v.

|

Output |

Definition at line 83 of file ahci_sata_layers.v.

|

Output |

Definition at line 84 of file ahci_sata_layers.v.

|

Output |

Definition at line 85 of file ahci_sata_layers.v.

|

Output |

Definition at line 86 of file ahci_sata_layers.v.

|

Output |

Definition at line 87 of file ahci_sata_layers.v.

|

Output |

Definition at line 89 of file ahci_sata_layers.v.

|

Output |

Definition at line 90 of file ahci_sata_layers.v.

|

Output |

Definition at line 91 of file ahci_sata_layers.v.

|

Output |

Definition at line 92 of file ahci_sata_layers.v.

|

Output |

Definition at line 93 of file ahci_sata_layers.v.

|

Output |

Definition at line 94 of file ahci_sata_layers.v.

|

Input |

Definition at line 96 of file ahci_sata_layers.v.

|

Input |

Definition at line 97 of file ahci_sata_layers.v.

|

Input |

Definition at line 101 of file ahci_sata_layers.v.

|

Input |

Definition at line 102 of file ahci_sata_layers.v.

|

Output |

Definition at line 104 of file ahci_sata_layers.v.

|

Output |

Definition at line 105 of file ahci_sata_layers.v.

|

Input |

Definition at line 106 of file ahci_sata_layers.v.

|

Input |

Definition at line 107 of file ahci_sata_layers.v.

|

Output |

Definition at line 110 of file ahci_sata_layers.v.

|

Output |

Definition at line 111 of file ahci_sata_layers.v.

|

Output |

Definition at line 112 of file ahci_sata_layers.v.

|

Output |

Definition at line 113 of file ahci_sata_layers.v.

|

Input |

Definition at line 117 of file ahci_sata_layers.v.

|

Input |

Definition at line 118 of file ahci_sata_layers.v.

|

Input |

Definition at line 119 of file ahci_sata_layers.v.

|

Input |

Definition at line 120 of file ahci_sata_layers.v.

|

Input |

Definition at line 121 of file ahci_sata_layers.v.

|

Input |

Definition at line 122 of file ahci_sata_layers.v.

|

Output |

Definition at line 123 of file ahci_sata_layers.v.

|

Output |

Definition at line 124 of file ahci_sata_layers.v.

|

Output |

Definition at line 126 of file ahci_sata_layers.v.

|

Output |

Definition at line 127 of file ahci_sata_layers.v.

|

Output |

Definition at line 128 of file ahci_sata_layers.v.

|

Input |

Definition at line 129 of file ahci_sata_layers.v.

|

Parameter |

Definition at line 133 of file ahci_sata_layers.v.

|

Parameter |

Definition at line 134 of file ahci_sata_layers.v.

|

Parameter |

Definition at line 136 of file ahci_sata_layers.v.

|

Parameter |

Definition at line 137 of file ahci_sata_layers.v.

|

Parameter |

Definition at line 138 of file ahci_sata_layers.v.

|

Parameter |

Definition at line 139 of file ahci_sata_layers.v.

|

Parameter |

Definition at line 141 of file ahci_sata_layers.v.

|

Parameter |

Definition at line 142 of file ahci_sata_layers.v.

|

Parameter |

Definition at line 143 of file ahci_sata_layers.v.

|

Signal |

Definition at line 145 of file ahci_sata_layers.v.

|

Signal |

Definition at line 146 of file ahci_sata_layers.v.

|

Signal |

Definition at line 147 of file ahci_sata_layers.v.

|

Signal |

Definition at line 148 of file ahci_sata_layers.v.

|

Signal |

Definition at line 149 of file ahci_sata_layers.v.

|

Signal |

Definition at line 150 of file ahci_sata_layers.v.

|

Signal |

Definition at line 151 of file ahci_sata_layers.v.

|

Signal |

Definition at line 153 of file ahci_sata_layers.v.

|

Signal |

Definition at line 154 of file ahci_sata_layers.v.

|

Signal |

Definition at line 155 of file ahci_sata_layers.v.

|

Signal |

Definition at line 156 of file ahci_sata_layers.v.

|

Signal |

Definition at line 157 of file ahci_sata_layers.v.

|

Signal |

Definition at line 158 of file ahci_sata_layers.v.

|

Signal |

Definition at line 160 of file ahci_sata_layers.v.

|

Signal |

Definition at line 161 of file ahci_sata_layers.v.

|

Signal |

Definition at line 163 of file ahci_sata_layers.v.

|

Signal |

Definition at line 164 of file ahci_sata_layers.v.

|

Signal |

Definition at line 165 of file ahci_sata_layers.v.

|

Signal |

Definition at line 166 of file ahci_sata_layers.v.

|

Signal |

Definition at line 169 of file ahci_sata_layers.v.

|

Signal |

Definition at line 171 of file ahci_sata_layers.v.

|

Signal |

Definition at line 172 of file ahci_sata_layers.v.

|

Signal |

Definition at line 173 of file ahci_sata_layers.v.

|

Signal |

Definition at line 174 of file ahci_sata_layers.v.

|

Signal |

Definition at line 175 of file ahci_sata_layers.v.

|

Signal |

Definition at line 177 of file ahci_sata_layers.v.

|

Signal |

Definition at line 178 of file ahci_sata_layers.v.

|

Signal |

Definition at line 179 of file ahci_sata_layers.v.

|

Signal |

Definition at line 180 of file ahci_sata_layers.v.

|

Signal |

Definition at line 181 of file ahci_sata_layers.v.

|

Signal |

Definition at line 183 of file ahci_sata_layers.v.

|

Signal |

Definition at line 184 of file ahci_sata_layers.v.

|

Signal |

Definition at line 185 of file ahci_sata_layers.v.

|

Signal |

Definition at line 186 of file ahci_sata_layers.v.

|

Signal |

Definition at line 187 of file ahci_sata_layers.v.

|

Signal |

Definition at line 188 of file ahci_sata_layers.v.

|

Signal |

Definition at line 189 of file ahci_sata_layers.v.

|

Signal |

Definition at line 191 of file ahci_sata_layers.v.

|

Signal |

Definition at line 192 of file ahci_sata_layers.v.

|

Signal |

Definition at line 193 of file ahci_sata_layers.v.

|

Signal |

Definition at line 195 of file ahci_sata_layers.v.

|

Signal |

Definition at line 196 of file ahci_sata_layers.v.

|

Signal |

Definition at line 197 of file ahci_sata_layers.v.

|

Signal |

Definition at line 199 of file ahci_sata_layers.v.

|

Signal |

Definition at line 200 of file ahci_sata_layers.v.

|

Signal |

Definition at line 202 of file ahci_sata_layers.v.

|

Signal |

Definition at line 238 of file ahci_sata_layers.v.

|

Signal |

Definition at line 239 of file ahci_sata_layers.v.

|

Signal |

Definition at line 250 of file ahci_sata_layers.v.

|

Signal |

Definition at line 251 of file ahci_sata_layers.v.

|

Module Instance |

Definition at line 415 of file ahci_sata_layers.v.

|

Module Instance |

Definition at line 449 of file ahci_sata_layers.v.

|

Module Instance |

Definition at line 483 of file ahci_sata_layers.v.

Definition at line 272 of file ahci_sata_layers.v.

|

Module Instance |

Definition at line 258 of file ahci_sata_layers.v.

|

Module Instance |

Definition at line 432 of file ahci_sata_layers.v.

|

Module Instance |

Definition at line 466 of file ahci_sata_layers.v.

|

Module Instance |

Definition at line 350 of file ahci_sata_layers.v.

The documentation for this Module was generated from the following files:

- x393_sata/ahci/ahci_sata_layers.v