Static Public Member Functions |

Always Constructs | |

| ALWAYS_415 | ( aclk or rst ) |

| ALWAYS_416 | ( rst or aclk ) |

| ALWAYS_417 | ( rst or aclk ) |

| ALWAYS_418 | ( rst or aclk ) |

| ALWAYS_419 | ( aclk ) |

| ALWAYS_420 | ( aclk or rst ) |

| ALWAYS_421 | ( rst or aclk ) |

Public Attributes |

Inputs | |

| rst | |

| aclk | |

| awaddr | [ 31 : 0 ] |

| awvalid | |

| awid | [ 5 : 0 ] |

| awlock | [ 1 : 0 ] |

| awcache | [ 3 : 0 ] |

| awprot | [ 2 : 0 ] |

| awlen | [ 3 : 0 ] |

| awsize | [ 1 : 0 ] |

| awburst | [ 1 : 0 ] |

| awqos | [ 3 : 0 ] |

| wdata | [ 63 : 0 ] |

| wvalid | |

| wid | [ 5 : 0 ] |

| wlast | |

| wstrb | [ 7 : 0 ] |

| bready | |

| wrissuecap1en | |

| sim_wr_ready | |

| sim_bresp_latency | [ 3 : 0 ] |

| reg_addr | [ 31 : 0 ] |

| reg_wr | |

| reg_rd | |

| reg_din | [ 31 : 0 ] |

Outputs | |

| aresetn | |

| awready | |

| wready | |

| bvalid | |

| bid | [ 5 : 0 ] |

| bresp | [ 1 : 0 ] |

| wcount | [ 7 : 0 ] |

| wacount | [ 5 : 0 ] |

| sim_wr_address | [ 31 : 0 ] |

| sim_wid | [ 5 : 0 ] |

| sim_wr_valid | |

| sim_wr_data | [ 63 : 0 ] |

| sim_wr_stb | [ 7 : 0 ] |

| sim_wr_cap | [ 2 : 0 ] |

| sim_wr_qos | [ 3 : 0 ] |

| reg_dout | [ 31 : 0 ] |

| reg_dvalid | |

Parameters | |

| HP_PORT | [ 1 : 0 ] 0 |

| AFI_BASECTRL | 32 'hf8008000+ (HP_PORT << 12 |

| AFI_WRCHAN_CTRL | AFI_BASECTRL + 'h14 |

| AFI_WRCHAN_ISSUINGCAP | AFI_BASECTRL + 'h18 |

| AFI_WRQOS | AFI_BASECTRL + 'h1c |

| AFI_WRDATAFIFO_LEVEL | AFI_BASECTRL + 'h20 |

| AFI_WRDEBUG | AFI_BASECTRL + 'h24 |

| VALID_AWLOCK | 2 'b0 |

| VALID_AWCACHE | 4 'b0011 |

| VALID_AWPROT | 3 'b000 |

| VALID_AWLOCK_MASK | 2 'b11 |

| VALID_AWCACHE_MASK | 4 'b0011 |

| VALID_AWPROT_MASK | 3 'b010 |

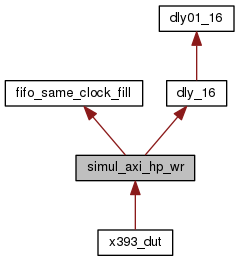

Module Instances | |

| fifo_same_clock_fill::waddr_i | Module fifo_same_clock_fill |

| fifo_same_clock_fill::wdata_i | Module fifo_same_clock_fill |

| dly_16::bresp_dly_16_i | Module dly_16 |

| fifo_same_clock_fill::wresp_ext_i | Module fifo_same_clock_fill |

| fifo_same_clock_fill::wresp_i | Module fifo_same_clock_fill |

Detailed Description

Definition at line 41 of file simul_axi_hp_wr.v.

Member Function Documentation

Definition at line 188 of file simul_axi_hp_wr.v.

Definition at line 220 of file simul_axi_hp_wr.v.

Definition at line 225 of file simul_axi_hp_wr.v.

Definition at line 231 of file simul_axi_hp_wr.v.

|

Always Construct |

Definition at line 260 of file simul_axi_hp_wr.v.

Definition at line 292 of file simul_axi_hp_wr.v.

Definition at line 394 of file simul_axi_hp_wr.v.

Member Data Documentation

|

Parameter |

Definition at line 42 of file simul_axi_hp_wr.v.

|

Input |

Definition at line 44 of file simul_axi_hp_wr.v.

|

Input |

Definition at line 46 of file simul_axi_hp_wr.v.

|

Output |

Definition at line 47 of file simul_axi_hp_wr.v.

|

Input |

Definition at line 49 of file simul_axi_hp_wr.v.

|

Input |

Definition at line 50 of file simul_axi_hp_wr.v.

|

Output |

Definition at line 51 of file simul_axi_hp_wr.v.

|

Input |

Definition at line 52 of file simul_axi_hp_wr.v.

|

Input |

Definition at line 53 of file simul_axi_hp_wr.v.

|

Input |

Definition at line 54 of file simul_axi_hp_wr.v.

|

Input |

Definition at line 55 of file simul_axi_hp_wr.v.

|

Input |

Definition at line 56 of file simul_axi_hp_wr.v.

|

Input |

Definition at line 57 of file simul_axi_hp_wr.v.

|

Input |

Definition at line 58 of file simul_axi_hp_wr.v.

|

Input |

Definition at line 59 of file simul_axi_hp_wr.v.

|

Input |

Definition at line 61 of file simul_axi_hp_wr.v.

|

Input |

Definition at line 62 of file simul_axi_hp_wr.v.

|

Output |

Definition at line 63 of file simul_axi_hp_wr.v.

|

Input |

Definition at line 64 of file simul_axi_hp_wr.v.

|

Input |

Definition at line 65 of file simul_axi_hp_wr.v.

|

Input |

Definition at line 66 of file simul_axi_hp_wr.v.

|

Output |

Definition at line 68 of file simul_axi_hp_wr.v.

|

Input |

Definition at line 69 of file simul_axi_hp_wr.v.

|

Output |

Definition at line 70 of file simul_axi_hp_wr.v.

|

Output |

Definition at line 71 of file simul_axi_hp_wr.v.

|

Output |

Definition at line 73 of file simul_axi_hp_wr.v.

|

Output |

Definition at line 74 of file simul_axi_hp_wr.v.

|

Input |

Definition at line 75 of file simul_axi_hp_wr.v.

|

Output |

Definition at line 77 of file simul_axi_hp_wr.v.

|

Output |

Definition at line 78 of file simul_axi_hp_wr.v.

|

Output |

Definition at line 79 of file simul_axi_hp_wr.v.

|

Input |

Definition at line 80 of file simul_axi_hp_wr.v.

|

Output |

Definition at line 81 of file simul_axi_hp_wr.v.

|

Output |

Definition at line 82 of file simul_axi_hp_wr.v.

|

Input |

Definition at line 83 of file simul_axi_hp_wr.v.

|

Output |

Definition at line 84 of file simul_axi_hp_wr.v.

|

Output |

Definition at line 85 of file simul_axi_hp_wr.v.

|

Input |

Definition at line 86 of file simul_axi_hp_wr.v.

|

Input |

Definition at line 87 of file simul_axi_hp_wr.v.

|

Input |

Definition at line 88 of file simul_axi_hp_wr.v.

|

Input |

Definition at line 89 of file simul_axi_hp_wr.v.

|

Output |

Definition at line 90 of file simul_axi_hp_wr.v.

|

Output |

Definition at line 91 of file simul_axi_hp_wr.v.

|

Parameter |

Definition at line 94 of file simul_axi_hp_wr.v.

|

Parameter |

Definition at line 95 of file simul_axi_hp_wr.v.

|

Parameter |

Definition at line 96 of file simul_axi_hp_wr.v.

|

Parameter |

Definition at line 97 of file simul_axi_hp_wr.v.

|

Parameter |

Definition at line 98 of file simul_axi_hp_wr.v.

|

Parameter |

Definition at line 99 of file simul_axi_hp_wr.v.

|

Parameter |

Definition at line 101 of file simul_axi_hp_wr.v.

|

Parameter |

Definition at line 102 of file simul_axi_hp_wr.v.

|

Parameter |

Definition at line 103 of file simul_axi_hp_wr.v.

|

Parameter |

Definition at line 104 of file simul_axi_hp_wr.v.

|

Parameter |

Definition at line 105 of file simul_axi_hp_wr.v.

|

Parameter |

Definition at line 106 of file simul_axi_hp_wr.v.

|

Signal |

Definition at line 117 of file simul_axi_hp_wr.v.

|

Signal |

Definition at line 118 of file simul_axi_hp_wr.v.

|

Signal |

Definition at line 119 of file simul_axi_hp_wr.v.

|

Signal |

Definition at line 120 of file simul_axi_hp_wr.v.

|

Signal |

Definition at line 121 of file simul_axi_hp_wr.v.

|

Signal |

Definition at line 122 of file simul_axi_hp_wr.v.

|

Signal |

Definition at line 123 of file simul_axi_hp_wr.v.

|

Signal |

Definition at line 124 of file simul_axi_hp_wr.v.

|

Signal |

Definition at line 125 of file simul_axi_hp_wr.v.

|

Signal |

Definition at line 127 of file simul_axi_hp_wr.v.

|

Signal |

Definition at line 128 of file simul_axi_hp_wr.v.

|

Signal |

Definition at line 130 of file simul_axi_hp_wr.v.

|

Signal |

Definition at line 131 of file simul_axi_hp_wr.v.

|

Signal |

Definition at line 132 of file simul_axi_hp_wr.v.

|

Signal |

Definition at line 133 of file simul_axi_hp_wr.v.

|

Signal |

Definition at line 134 of file simul_axi_hp_wr.v.

|

Signal |

Definition at line 135 of file simul_axi_hp_wr.v.

|

Signal |

Definition at line 136 of file simul_axi_hp_wr.v.

|

Signal |

Definition at line 137 of file simul_axi_hp_wr.v.

|

Signal |

Definition at line 140 of file simul_axi_hp_wr.v.

|

Signal |

Definition at line 141 of file simul_axi_hp_wr.v.

|

Signal |

Definition at line 142 of file simul_axi_hp_wr.v.

|

Signal |

Definition at line 143 of file simul_axi_hp_wr.v.

|

Signal |

Definition at line 144 of file simul_axi_hp_wr.v.

|

Signal |

Definition at line 145 of file simul_axi_hp_wr.v.

|

Signal |

Definition at line 146 of file simul_axi_hp_wr.v.

|

Signal |

Definition at line 147 of file simul_axi_hp_wr.v.

|

Signal |

Definition at line 148 of file simul_axi_hp_wr.v.

|

Signal |

Definition at line 150 of file simul_axi_hp_wr.v.

|

Signal |

Definition at line 151 of file simul_axi_hp_wr.v.

|

Signal |

Definition at line 152 of file simul_axi_hp_wr.v.

|

Signal |

Definition at line 153 of file simul_axi_hp_wr.v.

|

Signal |

Definition at line 154 of file simul_axi_hp_wr.v.

|

Signal |

Definition at line 155 of file simul_axi_hp_wr.v.

|

Signal |

Definition at line 156 of file simul_axi_hp_wr.v.

|

Signal |

Definition at line 157 of file simul_axi_hp_wr.v.

|

Signal |

Definition at line 158 of file simul_axi_hp_wr.v.

|

Signal |

Definition at line 160 of file simul_axi_hp_wr.v.

|

Signal |

Definition at line 161 of file simul_axi_hp_wr.v.

|

Signal |

Definition at line 162 of file simul_axi_hp_wr.v.

|

Signal |

Definition at line 164 of file simul_axi_hp_wr.v.

|

Signal |

Definition at line 165 of file simul_axi_hp_wr.v.

|

Signal |

Definition at line 354 of file simul_axi_hp_wr.v.

|

Signal |

Definition at line 355 of file simul_axi_hp_wr.v.

|

Signal |

Definition at line 357 of file simul_axi_hp_wr.v.

|

Signal |

Definition at line 358 of file simul_axi_hp_wr.v.

|

Module Instance |

Definition at line 362 of file simul_axi_hp_wr.v.

|

Module Instance |

Definition at line 317 of file simul_axi_hp_wr.v.

|

Module Instance |

Definition at line 335 of file simul_axi_hp_wr.v.

|

Module Instance |

Definition at line 374 of file simul_axi_hp_wr.v.

|

Module Instance |

Definition at line 400 of file simul_axi_hp_wr.v.

The documentation for this Module was generated from the following files:

- simulation_modules/simul_axi_hp_wr.v