Public Attributes |

Inputs | |

| pxclk_out | |

| pxclk_en | |

| rst | |

| mclk | |

| dly_data | [ 7 : 0 ] |

| set_idelay | |

| ld_idelay | |

Inouts | |

| pxclk | |

Outputs | |

| pxclk_in | |

Parameters | |

| IODELAY_GRP | "IODELAY_SENSOR" |

| IDELAY_VALUE | integer 0 |

| PXD_DRIVE | integer 12 |

| PXD_IBUF_LOW_PWR | "TRUE" |

| PXD_IOSTANDARD | "DEFAULT" |

| PXD_SLEW | "SLOW" |

| REFCLK_FREQUENCY | real 300 . 0 |

| HIGH_PERFORMANCE_MODE | "FALSE" |

Signals | |

| wire | pxclk_iobuf |

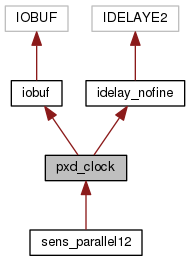

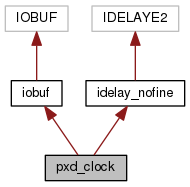

Module Instances | |

| iobuf::iobuf_pxclk_i | Module iobuf |

| idelay_nofine::pxclk_dly_i | Module idelay_nofine |

Detailed Description

Definition at line 41 of file pxd_clock.v.

Member Data Documentation

|

Parameter |

Definition at line 42 of file pxd_clock.v.

|

Parameter |

Definition at line 43 of file pxd_clock.v.

|

Parameter |

Definition at line 44 of file pxd_clock.v.

|

Parameter |

Definition at line 45 of file pxd_clock.v.

|

Parameter |

Definition at line 46 of file pxd_clock.v.

|

Parameter |

Definition at line 47 of file pxd_clock.v.

|

Parameter |

Definition at line 48 of file pxd_clock.v.

|

Parameter |

Definition at line 49 of file pxd_clock.v.

|

Inout |

Definition at line 52 of file pxd_clock.v.

|

Input |

Definition at line 53 of file pxd_clock.v.

|

Input |

Definition at line 54 of file pxd_clock.v.

|

Output |

Definition at line 55 of file pxd_clock.v.

|

Input |

Definition at line 56 of file pxd_clock.v.

|

Input |

Definition at line 57 of file pxd_clock.v.

|

Input |

Definition at line 58 of file pxd_clock.v.

|

Input |

Definition at line 59 of file pxd_clock.v.

|

Input |

Definition at line 60 of file pxd_clock.v.

|

Signal |

Definition at line 62 of file pxd_clock.v.

|

Module Instance |

Definition at line 92 of file pxd_clock.v.

|

Module Instance |

Definition at line 64 of file pxd_clock.v.

The documentation for this Module was generated from the following files:

- sensor/pxd_clock.v