oddr_ss Module Reference

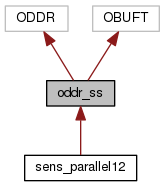

Inheritance diagram for oddr_ss:

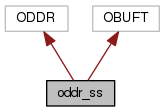

Collaboration diagram for oddr_ss:

Public Attributes |

Inputs | |

| clk | |

| ce | |

| rst | |

| set | |

| din | [ 1 : 0 ] |

| tin | |

Outputs | |

| dq | |

Parameters | |

| IOSTANDARD | "DEFAULT" |

| SLEW | "SLOW" |

| DDR_CLK_EDGE | "OPPOSITE_EDGE" |

| INIT | 1 'b0 |

| SRTYPE | "SYNC" |

Signals | |

| wire | idq |

Module Instances | |

| ODDR::ODDR_i | Module ODDR |

| OBUFT::iobufs_i | Module OBUFT |

Detailed Description

Member Data Documentation

|

Parameter |

|

Parameter |

The documentation for this Module was generated from the following files:

- wrap/oddr_ss.v