Static Public Member Functions |

Always Constructs | |

| ALWAYS_38 | ( iclk ) |

| ALWAYS_39 | ( mclk ) |

Public Attributes |

Inputs | |

| mclk | |

| en | |

| iclk | |

| data_in | [ 1 << MULT_SAXI_WLOG - 1 : 0 ] |

| valid | |

| read_burst | |

Outputs | |

| has_burst | reg |

| data_out | [ 31 : 0 ] |

| pre_valid_chn | |

Parameters | |

| MULT_SAXI_HALF_BRAM_IN | 1 |

| MULT_SAXI_BSLOG | 4 |

| MULT_SAXI_WLOG | 4 |

| INA_WIDTH | (MULT_SAXI_HALF_BRAM_IN ? 14 : 15 ) - MULT_SAXI_WLOG |

| OUTA_WIDTH | (MULT_SAXI_HALF_BRAM_IN ? 14 : 15 ) - 5 |

| INW_CNTR_WIDTH | MULT_SAXI_BSLOG + 5 -MULT_SAXI_WLOG |

| OUTW_CNTR_WIDTH | MULT_SAXI_BSLOG |

| BURST_WIDTH | OUTA_WIDTH - OUTW_CNTR_WIDTH |

GENERATE | |

| GENERATE [120] | |

Signals | |

| reg | en_iclk |

| reg[INW_CNTR_WIDTH - 1 : 0 ] | inw_cntr |

| reg[BURST_WIDTH - 1 : 0 ] | in_burst |

| reg[OUTW_CNTR_WIDTH - 1 : 0 ] | outw_cntr |

| reg[BURST_WIDTH - 1 : 0 ] | out_burst |

| reg[BURST_WIDTH : 0 ] | num_out_bursts |

| wire[INA_WIDTH - 1 : 0 ] | waddr |

| wire[OUTA_WIDTH - 1 : 0 ] | raddr |

| wire | put_burst_mclk |

| wire | wr_last_word |

| wire | re_last_word |

| reg[ 1 : 0 ] | buf_re |

Module Instances | |

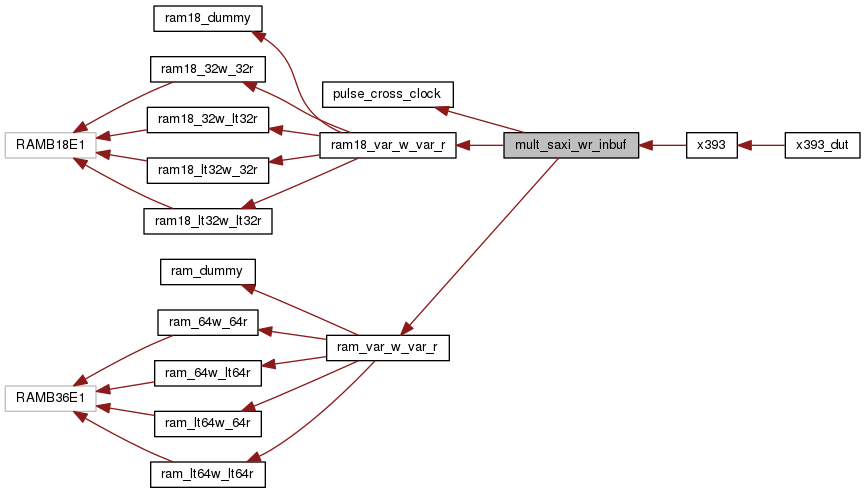

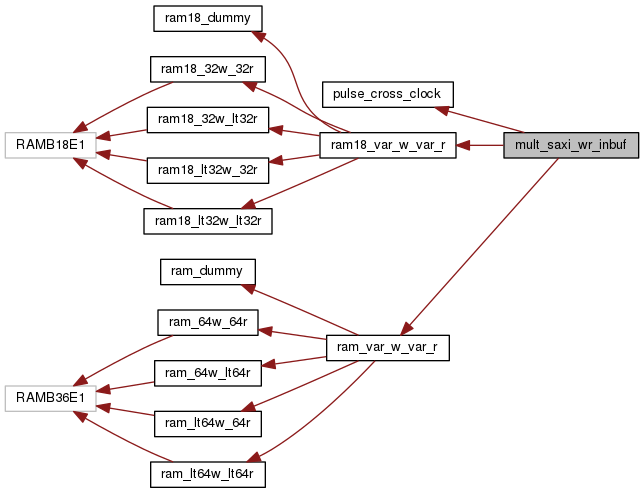

| pulse_cross_clock::put_burst_mclk_i | Module pulse_cross_clock |

| ram18_var_w_var_r::ram_var_w_var_r_i | Module ram18_var_w_var_r [generate] |

| ram_var_w_var_r::ram_var_w_var_r_i | Module ram_var_w_var_r [generate] |

Detailed Description

Definition at line 41 of file mult_saxi_wr_inbuf.v.

Member Function Documentation

|

Always Construct |

Definition at line 83 of file mult_saxi_wr_inbuf.v.

|

Always Construct |

Definition at line 93 of file mult_saxi_wr_inbuf.v.

Member Data Documentation

|

Parameter |

Definition at line 42 of file mult_saxi_wr_inbuf.v.

|

Parameter |

Definition at line 43 of file mult_saxi_wr_inbuf.v.

|

Parameter |

Definition at line 44 of file mult_saxi_wr_inbuf.v.

|

Input |

Definition at line 46 of file mult_saxi_wr_inbuf.v.

|

Input |

Definition at line 47 of file mult_saxi_wr_inbuf.v.

|

Input |

Definition at line 50 of file mult_saxi_wr_inbuf.v.

|

Input |

Definition at line 51 of file mult_saxi_wr_inbuf.v.

|

Input |

Definition at line 52 of file mult_saxi_wr_inbuf.v.

|

Output |

Definition at line 54 of file mult_saxi_wr_inbuf.v.

|

Input |

Definition at line 55 of file mult_saxi_wr_inbuf.v.

|

Output |

Definition at line 56 of file mult_saxi_wr_inbuf.v.

|

Output |

Definition at line 57 of file mult_saxi_wr_inbuf.v.

|

Parameter |

Definition at line 60 of file mult_saxi_wr_inbuf.v.

|

Parameter |

Definition at line 61 of file mult_saxi_wr_inbuf.v.

|

Parameter |

Definition at line 62 of file mult_saxi_wr_inbuf.v.

|

Parameter |

Definition at line 63 of file mult_saxi_wr_inbuf.v.

|

Parameter |

Definition at line 64 of file mult_saxi_wr_inbuf.v.

|

Signal |

Definition at line 66 of file mult_saxi_wr_inbuf.v.

|

Signal |

Definition at line 67 of file mult_saxi_wr_inbuf.v.

|

Signal |

Definition at line 68 of file mult_saxi_wr_inbuf.v.

|

Signal |

Definition at line 69 of file mult_saxi_wr_inbuf.v.

|

Signal |

Definition at line 70 of file mult_saxi_wr_inbuf.v.

|

Signal |

Definition at line 71 of file mult_saxi_wr_inbuf.v.

|

Signal |

Definition at line 73 of file mult_saxi_wr_inbuf.v.

|

Signal |

Definition at line 74 of file mult_saxi_wr_inbuf.v.

|

Signal |

Definition at line 76 of file mult_saxi_wr_inbuf.v.

|

Signal |

Definition at line 77 of file mult_saxi_wr_inbuf.v.

|

Signal |

Definition at line 79 of file mult_saxi_wr_inbuf.v.

|

Signal |

Definition at line 80 of file mult_saxi_wr_inbuf.v.

|

GENERATE |

Definition at line 120 of file mult_saxi_wr_inbuf.v.

|

Module Instance |

Definition at line 112 of file mult_saxi_wr_inbuf.v.

|

Module Instance |

Definition at line 122 of file mult_saxi_wr_inbuf.v.

|

Module Instance |

Definition at line 140 of file mult_saxi_wr_inbuf.v.

The documentation for this Module was generated from the following files: