Static Public Member Functions |

Always Constructs | |

| ALWAYS_504 | ( wclk or rst ) |

| ALWAYS_505 | ( rclk or rst ) |

| ALWAYS_506 | ( rclk ) |

| ALWAYS_507 | ( wclk ) |

Public Attributes |

Inputs | |

| rst | |

| rrst | |

| wrst | |

| rclk | |

| wclk | |

| we | |

| re | |

| data_in | [DATA_WIDTH - 1 : 0 ] |

Outputs | |

| data_out | [DATA_WIDTH - 1 : 0 ] |

| nempty | |

| half_empty | |

Parameters | |

| DATA_WIDTH | integer 16 |

| DATA_DEPTH | integer 4 |

| DATA_2DEPTH | integer (1<<DATA_DEPTH)- 1 |

Signals | |

| reg[DATA_WIDTH - 1 : 0 ] | ram [ 0 :DATA_2DEPTH ] |

| reg[DATA_DEPTH - 1 : 0 ] | raddr |

| reg[DATA_DEPTH - 1 : 0 ] | waddr |

| reg[DATA_DEPTH - 1 : 0 ] | waddr_gray |

| reg[DATA_DEPTH - 1 : 0 ] | waddr_gray_rclk |

| wire[DATA_DEPTH - 1 : 0 ] | waddr_plus1 |

| wire[DATA_DEPTH - 1 : 0 ] | waddr_plus1_gray |

| wire[DATA_DEPTH - 1 : 0 ] | raddr_gray |

| wire[DATA_DEPTH - 1 : 0 ] | raddr_plus1 |

| wire[ 2 : 0 ] | raddr_plus1_gray_top3 |

| reg[ 2 : 0 ] | raddr_gray_top3 |

| reg[ 2 : 0 ] | raddr_gray_top3_wclk |

| wire[ 2 : 0 ] | raddr_top3_wclk |

| wire[ 2 : 0 ] | waddr_top3 |

| wire[ 2 : 0 ] | addr_diff |

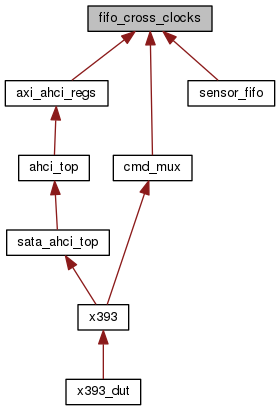

Detailed Description

Definition at line 41 of file fifo_cross_clocks.v.

Member Function Documentation

Definition at line 91 of file fifo_cross_clocks.v.

Definition at line 102 of file fifo_cross_clocks.v.

|

Always Construct |

Definition at line 113 of file fifo_cross_clocks.v.

|

Always Construct |

Definition at line 118 of file fifo_cross_clocks.v.

Member Data Documentation

|

Parameter |

Definition at line 43 of file fifo_cross_clocks.v.

|

Parameter |

Definition at line 44 of file fifo_cross_clocks.v.

|

Input |

Definition at line 46 of file fifo_cross_clocks.v.

|

Input |

Definition at line 47 of file fifo_cross_clocks.v.

|

Input |

Definition at line 48 of file fifo_cross_clocks.v.

|

Input |

Definition at line 49 of file fifo_cross_clocks.v.

|

Input |

Definition at line 50 of file fifo_cross_clocks.v.

|

Input |

Definition at line 51 of file fifo_cross_clocks.v.

|

Input |

Definition at line 52 of file fifo_cross_clocks.v.

|

Input |

Definition at line 53 of file fifo_cross_clocks.v.

|

Output |

Definition at line 54 of file fifo_cross_clocks.v.

|

Output |

Definition at line 55 of file fifo_cross_clocks.v.

|

Output |

Definition at line 56 of file fifo_cross_clocks.v.

|

Parameter |

Definition at line 58 of file fifo_cross_clocks.v.

|

Signal |

Definition at line 59 of file fifo_cross_clocks.v.

|

Signal |

Definition at line 60 of file fifo_cross_clocks.v.

|

Signal |

Definition at line 61 of file fifo_cross_clocks.v.

|

Signal |

Definition at line 62 of file fifo_cross_clocks.v.

|

Signal |

Definition at line 63 of file fifo_cross_clocks.v.

|

Signal |

Definition at line 64 of file fifo_cross_clocks.v.

|

Signal |

Definition at line 65 of file fifo_cross_clocks.v.

|

Signal |

Definition at line 67 of file fifo_cross_clocks.v.

|

Signal |

Definition at line 68 of file fifo_cross_clocks.v.

|

Signal |

Definition at line 69 of file fifo_cross_clocks.v.

|

Signal |

Definition at line 70 of file fifo_cross_clocks.v.

|

Signal |

Definition at line 71 of file fifo_cross_clocks.v.

|

Signal |

Definition at line 72 of file fifo_cross_clocks.v.

|

Signal |

Definition at line 76 of file fifo_cross_clocks.v.

|

Signal |

Definition at line 77 of file fifo_cross_clocks.v.

The documentation for this Module was generated from the following files:

- util_modules/fifo_cross_clocks.v