cmd_mux Module Reference

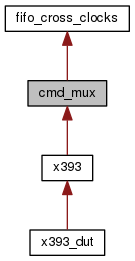

Inheritance diagram for cmd_mux:

Collaboration diagram for cmd_mux:

Static Public Member Functions |

Always Constructs | |

| ALWAYS_482 | ( axi_clk ) |

| ALWAYS_483 | ( ** ) |

| ALWAYS_484 | ( mclk ) |

| ALWAYS_485 | ( mclk ) |

| ALWAYS_486 | ( mclk ) |

| ALWAYS_487 | ( mclk ) |

| ALWAYS_488 | ( mclk ) |

Public Attributes |

Inputs | |

| axi_clk | |

| mclk | |

| mrst | |

| arst | |

| pre_waddr | [AXI_WR_ADDR_BITS - 1 : 0 ] |

| start_wburst | |

| waddr | [AXI_WR_ADDR_BITS - 1 : 0 ] |

| wr_en | |

| wdata | [ 31 : 0 ] |

| cseq_waddr | [AXI_WR_ADDR_BITS - 1 : 0 ] |

| cseq_wr_en | |

| cseq_wdata | [ 31 : 0 ] |

Outputs | |

| busy | |

| cseq_ackn | |

| par_waddr | [AXI_WR_ADDR_BITS - 1 : 0 ] |

| par_data | [ 31 : 0 ] |

| byte_ad | [ 7 : 0 ] |

| ad_stb | |

Parameters | |

| AXI_WR_ADDR_BITS | 14 |

| CONTROL_ADDR | 'h0000 |

| CONTROL_ADDR_MASK | 'h3800 |

| NUM_CYCLES_LOW_BIT | 6 |

| NUM_CYCLES_00 | 2 |

| NUM_CYCLES_01 | 4 |

| NUM_CYCLES_02 | 3 |

| NUM_CYCLES_03 | 3 |

| NUM_CYCLES_04 | 6 |

| NUM_CYCLES_05 | 6 |

| NUM_CYCLES_06 | 4 |

| NUM_CYCLES_07 | 4 |

| NUM_CYCLES_08 | 6 |

| NUM_CYCLES_09 | 6 |

| NUM_CYCLES_10 | 6 |

| NUM_CYCLES_11 | 6 |

| NUM_CYCLES_12 | 6 |

| NUM_CYCLES_13 | 5 |

| NUM_CYCLES_14 | 6 |

| NUM_CYCLES_15 | 9 |

| NUM_CYCLES_16 | 6 |

| NUM_CYCLES_17 | 6 |

| NUM_CYCLES_18 | 6 |

| NUM_CYCLES_19 | 6 |

| NUM_CYCLES_20 | 6 |

| NUM_CYCLES_21 | 6 |

| NUM_CYCLES_22 | 6 |

| NUM_CYCLES_23 | 6 |

| NUM_CYCLES_24 | 6 |

| NUM_CYCLES_25 | 6 |

| NUM_CYCLES_26 | 6 |

| NUM_CYCLES_27 | 6 |

| NUM_CYCLES_28 | 6 |

| NUM_CYCLES_29 | 6 |

| NUM_CYCLES_30 | 6 |

| NUM_CYCLES_31 | 6 |

Signals | |

| reg | busy_r |

| reg | selected |

| wire | fifo_half_empty |

| wire | selected_w |

| wire | ss |

| reg[ 47 : 0 ] | par_ad |

| reg | ad_stb_r |

| reg | cmdseq_full_r |

| reg[AXI_WR_ADDR_BITS - 1 : 0 ] | cseq_waddr_r |

| reg[ 31 : 0 ] | cseq_wdata_r |

| reg[ 3 : 0 ] | seq_length |

| reg[ 4 : 0 ] | seq_busy_r |

| wire[ 4 : 0 ] | seq_length_rom_a |

| wire | can_start_w |

| wire | start_w |

| wire | start_axi_w |

| wire | fifo_nempty |

| wire[AXI_WR_ADDR_BITS - 1 : 0 ] | waddr_fifo_out |

| wire[ 31 : 0 ] | wdata_fifo_out |

Module Instances | |

| fifo_cross_clocks::fifo_cross_clocks_i | Module fifo_cross_clocks |

Detailed Description

Member Function Documentation

Member Data Documentation

|

Parameter |

|

Parameter |

|

Parameter |

|

Parameter |

|

Parameter |

|

Parameter |

|

Parameter |

|

Parameter |

|

Parameter |

|

Parameter |

|

Parameter |

|

Parameter |

|

Parameter |

|

Parameter |

|

Parameter |

|

Parameter |

|

Parameter |

|

Parameter |

|

Parameter |

|

Parameter |

|

Parameter |

|

Parameter |

|

Parameter |

|

Parameter |

|

Parameter |

|

Parameter |

|

Parameter |

|

Parameter |

|

Parameter |

|

Parameter |

|

Parameter |

|

Parameter |

|

Parameter |

|

Parameter |

|

Parameter |

|

Parameter |

|

Input |

|

Input |

|

Input |

|

Input |

|

Input |

|

Input |

|

Output |

|

Signal |

|

Signal |

|

Signal |

|

Signal |

|

Signal |

|

Signal |

|

Signal |

|

Signal |

|

Signal |

|

Signal |

|

Signal |

|

Signal |

|

Signal |

|

Module Instance |

The documentation for this Module was generated from the following files:

- util_modules/cmd_mux.v