Static Public Member Functions |

Always Constructs | |

| ALWAYS_2 | ( aclk ) |

| ALWAYS_3 | ( aclk ) |

Public Attributes |

Inputs | |

| aclk | |

| arst | |

| awaddr | [ 31 : 0 ] |

| awvalid | |

| awid | [ 11 : 0 ] |

| awlen | [ 3 : 0 ] |

| awsize | [ 1 : 0 ] |

| awburst | [ 1 : 0 ] |

| wdata | [ 31 : 0 ] |

| wvalid | |

| wid | [ 11 : 0 ] |

| wlast | |

| wstb | [ 3 : 0 ] |

| bready | |

| dev_ready | |

Outputs | |

| awready | |

| wready | |

| bvalid | |

| bid | [ 11 : 0 ] |

| bresp | [ 1 : 0 ] |

| pre_awaddr | [ADDRESS_BITS - 1 : 0 ] |

| start_burst | |

| bram_wclk | |

| bram_waddr | [ADDRESS_BITS - 1 : 0 ] |

| pre_bram_wen | |

| bram_wen | |

| bram_wstb | [ 3 : 0 ] |

| bram_wdata | [ 31 : 0 ] |

Parameters | |

| ADDRESS_BITS | 10 |

Signals | |

| wire | aw_nempty |

| wire | aw_half_full |

| wire[ 1 : 0 ] | awburst_out |

| wire[ 1 : 0 ] | awsize_out |

| wire[ 3 : 0 ] | awlen_out |

| wire[ADDRESS_BITS - 1 : 0 ] | awaddr_out |

| wire[ 11 : 0 ] | awid_out |

| wire | w_nempty |

| wire | w_half_full |

| wire[ 31 : 0 ] | wdata_out |

| wire | wlast_out |

| wire[ 3 : 0 ] | wstb_out |

| wire[ 11 : 0 ] | wid_out |

| reg | write_in_progress |

| reg[ADDRESS_BITS - 1 : 0 ] | write_address |

| reg[ 3 : 0 ] | write_left |

| reg[ 1 : 0 ] | wburst |

| reg[ 3 : 0 ] | wlen |

| wire[ADDRESS_BITS - 1 : 0 ] | next_wr_address_w |

| wire | bram_we_w |

| wire | start_write_burst_w |

| wire | write_in_progress_w |

| wire | aw_nempty_ready |

| wire | w_nempty_ready |

| reg | dev_ready_r |

| wire[ 1 : 0 ] | bresp_in |

| reg | was_bresp_re |

| wire | bresp_re |

Module Instances | |

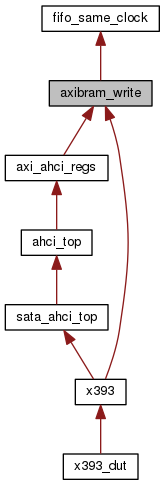

| fifo_same_clock::waddr_i | Module fifo_same_clock |

| fifo_same_clock::wdata_i | Module fifo_same_clock |

| fifo_same_clock::wresp_i | Module fifo_same_clock |

Detailed Description

Definition at line 43 of file axibram_write.v.

Member Function Documentation

|

Always Construct |

Definition at line 149 of file axibram_write.v.

|

Always Construct |

Definition at line 215 of file axibram_write.v.

Member Data Documentation

|

Signal |

Definition at line 121 of file axibram_write.v.

|

Signal |

Definition at line 123 of file axibram_write.v.

|

Signal |

Definition at line 124 of file axibram_write.v.

|

Signal |

Definition at line 125 of file axibram_write.v.

|

Signal |

Definition at line 126 of file axibram_write.v.

|

Signal |

Definition at line 127 of file axibram_write.v.

|

Signal |

Definition at line 128 of file axibram_write.v.

|

Signal |

Definition at line 130 of file axibram_write.v.

|

Signal |

Definition at line 131 of file axibram_write.v.

|

Signal |

Definition at line 135 of file axibram_write.v.

|

Signal |

Definition at line 171 of file axibram_write.v.

|

Signal |

Definition at line 212 of file axibram_write.v.

|

Signal |

Definition at line 213 of file axibram_write.v.

|

Parameter |

Definition at line 44 of file axibram_write.v.

|

Input |

Definition at line 46 of file axibram_write.v.

|

Input |

Definition at line 47 of file axibram_write.v.

|

Input |

Definition at line 50 of file axibram_write.v.

|

Input |

Definition at line 51 of file axibram_write.v.

|

Output |

Definition at line 52 of file axibram_write.v.

|

Input |

Definition at line 53 of file axibram_write.v.

|

Input |

Definition at line 54 of file axibram_write.v.

|

Input |

Definition at line 55 of file axibram_write.v.

|

Input |

Definition at line 56 of file axibram_write.v.

|

Input |

Definition at line 58 of file axibram_write.v.

|

Input |

Definition at line 59 of file axibram_write.v.

|

Output |

Definition at line 60 of file axibram_write.v.

|

Input |

Definition at line 61 of file axibram_write.v.

|

Input |

Definition at line 62 of file axibram_write.v.

|

Input |

Definition at line 63 of file axibram_write.v.

|

Output |

Definition at line 65 of file axibram_write.v.

|

Input |

Definition at line 66 of file axibram_write.v.

|

Output |

Definition at line 67 of file axibram_write.v.

|

Output |

Definition at line 68 of file axibram_write.v.

|

Output |

Definition at line 71 of file axibram_write.v.

|

Output |

Definition at line 72 of file axibram_write.v.

|

Input |

Definition at line 73 of file axibram_write.v.

|

Output |

Definition at line 75 of file axibram_write.v.

|

Output |

Definition at line 76 of file axibram_write.v.

|

Output |

Definition at line 77 of file axibram_write.v.

|

Output |

Definition at line 78 of file axibram_write.v.

|

Output |

Definition at line 79 of file axibram_write.v.

|

Output |

Definition at line 80 of file axibram_write.v.

|

Signal |

Definition at line 101 of file axibram_write.v.

|

Signal |

Definition at line 102 of file axibram_write.v.

|

Signal |

Definition at line 104 of file axibram_write.v.

|

Signal |

Definition at line 106 of file axibram_write.v.

|

Signal |

Definition at line 107 of file axibram_write.v.

|

Signal |

Definition at line 108 of file axibram_write.v.

|

Signal |

Definition at line 110 of file axibram_write.v.

|

Signal |

Definition at line 111 of file axibram_write.v.

|

Signal |

Definition at line 112 of file axibram_write.v.

|

Signal |

Definition at line 114 of file axibram_write.v.

|

Signal |

Definition at line 116 of file axibram_write.v.

|

Signal |

Definition at line 117 of file axibram_write.v.

|

Signal |

Definition at line 118 of file axibram_write.v.

|

Signal |

Definition at line 119 of file axibram_write.v.

|

Signal |

Definition at line 120 of file axibram_write.v.

|

Module Instance |

Definition at line 185 of file axibram_write.v.

|

Module Instance |

Definition at line 198 of file axibram_write.v.

|

Module Instance |

Definition at line 220 of file axibram_write.v.

The documentation for this Module was generated from the following files:

- axi/axibram_write.v