Static Public Member Functions |

Always Constructs | |

| ALWAYS_732 | ( usrclk ) |

| ALWAYS_733 | ( usrclk ) |

Public Attributes |

Inputs | |

| usrclk | wire |

| usrclk2 | wire |

| reset | wire |

| indata | wire [internal_data_width - 1 : 0 ] |

| inisk | wire [internal_isk_width - 1 : 0 ] |

| realign | wire |

Outputs | |

| outdata | wire [interface_data_width - 1 : 0 ] |

| outisk | wire [interface_isk_width - 1 : 0 ] |

GENERATE | |

| GENERATE [1787] | |

| GENERATE [1794] | |

| GENERATE [1819] | |

Signals | |

| reg[interface_data_width - 1 : 0 ] | inbuffer_data |

| reg[interface_isk_width - 1 : 0 ] | inbuffer_isk |

| reg[ 31 : 0 ] | wordcounter |

| wire | empty_rd |

| wire | full_wr |

| wire | val_wr |

| wire | val_rd |

| wire | almost_empty_rd |

| reg | need_reset |

| [interface_total_width - 1 : 0 ] | resync |

| wire[interface_total_width - 1 : 0 ] | data_wr |

Module Instances | |

| resync_fifo_nonsynt::fifo | Module resync_fifo_nonsynt |

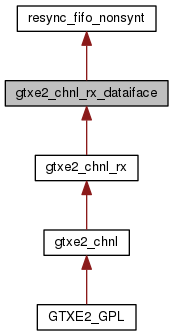

Detailed Description

Definition at line 1752 of file GTXE2_GPL.v.

Member Function Documentation

|

Always Construct |

Definition at line 1783 of file GTXE2_GPL.v.

|

Always Construct |

Definition at line 1805 of file GTXE2_GPL.v.

Member Data Documentation

|

Parameter |

Definition at line 1753 of file GTXE2_GPL.v.

|

Parameter |

Definition at line 1754 of file GTXE2_GPL.v.

|

Parameter |

Definition at line 1755 of file GTXE2_GPL.v.

|

Parameter |

Definition at line 1756 of file GTXE2_GPL.v.

|

Input |

Definition at line 1759 of file GTXE2_GPL.v.

|

Input |

Definition at line 1760 of file GTXE2_GPL.v.

|

Input |

Definition at line 1761 of file GTXE2_GPL.v.

|

Output |

Definition at line 1762 of file GTXE2_GPL.v.

|

Output |

Definition at line 1763 of file GTXE2_GPL.v.

|

Input |

Definition at line 1764 of file GTXE2_GPL.v.

|

Input |

Definition at line 1765 of file GTXE2_GPL.v.

|

Input |

Definition at line 1766 of file GTXE2_GPL.v.

|

Parameter |

Definition at line 1769 of file GTXE2_GPL.v.

Definition at line 1770 of file GTXE2_GPL.v.

Definition at line 1771 of file GTXE2_GPL.v.

|

Signal |

Definition at line 1773 of file GTXE2_GPL.v.

|

Signal |

Definition at line 1774 of file GTXE2_GPL.v.

|

Signal |

Definition at line 1775 of file GTXE2_GPL.v.

|

Signal |

Definition at line 1776 of file GTXE2_GPL.v.

|

Signal |

Definition at line 1777 of file GTXE2_GPL.v.

|

Signal |

Definition at line 1778 of file GTXE2_GPL.v.

|

Signal |

Definition at line 1779 of file GTXE2_GPL.v.

|

Signal |

Definition at line 1780 of file GTXE2_GPL.v.

|

Signal |

Definition at line 1781 of file GTXE2_GPL.v.

|

Signal |

Definition at line 1814 of file GTXE2_GPL.v.

|

Signal |

Definition at line 1818 of file GTXE2_GPL.v.

|

GENERATE |

Definition at line 1787 of file GTXE2_GPL.v.

|

GENERATE |

Definition at line 1794 of file GTXE2_GPL.v.

|

GENERATE |

Definition at line 1819 of file GTXE2_GPL.v.

|

Module Instance |

Definition at line 1826 of file GTXE2_GPL.v.

The documentation for this Module was generated from the following files:

- x393_sata/wrapper/GTXE2_GPL.v