Static Public Member Functions |

Always Constructs | |

| ALWAYS_496 | ( mclk ) |

Public Attributes |

Inputs | |

| mclk | |

| mrst | |

| cmd_ad | [ 7 : 0 ] |

| cmd_stb | |

| status_start | |

| debug_di | |

Outputs | |

| status_ad | [ 7 : 0 ] |

| status_rq | |

| debug_do | |

| debug_sl | |

Parameters | |

| DEBUG_ADDR | 'h710 |

| DEBUG_MASK | 'h7fc |

| DEBUG_STATUS_REG_ADDR | 'hfc |

| DEBUG_READ_REG_ADDR | 'hfd |

| DEBUG_SHIFT_DATA | 'h0 |

| DEBUG_LOAD | 'h1 |

| DEBUG_SET_STATUS | 'h2 |

| DEBUG_CMD_LATENCY | 2 |

Signals | |

| wire[ 1 : 0 ] | cmd_a |

| wire[ 31 : 0 ] | cmd_data |

| wire | cmd_we |

| reg[ 31 : 0 ] | data_sr |

| reg | tgl |

| reg[ 6 : 0 ] | cntr |

| reg | ld_r |

| reg | cmd |

| reg[DEBUG_CMD_LATENCY : 0 ] | cmd_reg |

| wire[ 3 : 0 ] | debug_latency_plus1 |

| wire | set_status_w |

| wire | shift32_w |

| wire | load_w |

| wire | cmd_reg_dly |

| wire | shift_done |

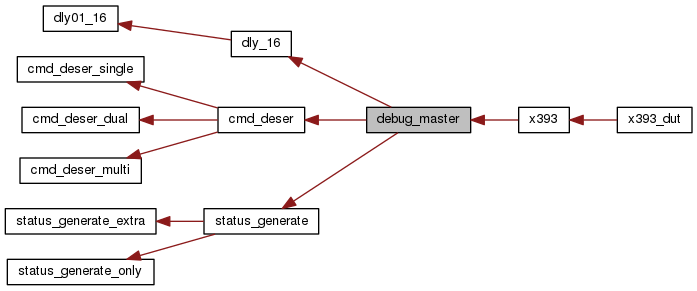

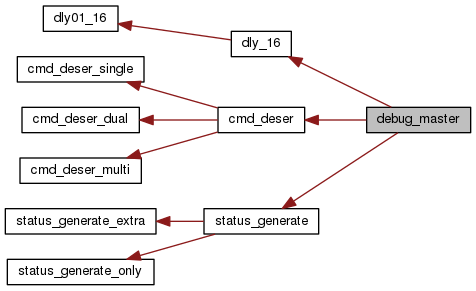

Module Instances | |

| dly_16::dly_16_i | Module dly_16 |

| cmd_deser::cmd_deser_32bit_i | Module cmd_deser |

| status_generate::status_generate_i | Module status_generate |

Detailed Description

Definition at line 41 of file debug_master.v.

Member Function Documentation

|

Always Construct |

Definition at line 86 of file debug_master.v.

Member Data Documentation

|

Parameter |

Definition at line 42 of file debug_master.v.

|

Parameter |

Definition at line 43 of file debug_master.v.

|

Parameter |

Definition at line 44 of file debug_master.v.

|

Parameter |

Definition at line 45 of file debug_master.v.

|

Parameter |

Definition at line 46 of file debug_master.v.

|

Parameter |

Definition at line 47 of file debug_master.v.

|

Parameter |

Definition at line 48 of file debug_master.v.

|

Parameter |

Definition at line 49 of file debug_master.v.

|

Input |

Definition at line 51 of file debug_master.v.

|

Input |

Definition at line 52 of file debug_master.v.

|

Input |

Definition at line 54 of file debug_master.v.

|

Input |

Definition at line 55 of file debug_master.v.

|

Output |

Definition at line 57 of file debug_master.v.

|

Output |

Definition at line 58 of file debug_master.v.

|

Input |

Definition at line 59 of file debug_master.v.

|

Output |

Definition at line 62 of file debug_master.v.

|

Output |

Definition at line 63 of file debug_master.v.

|

Input |

Definition at line 64 of file debug_master.v.

|

Signal |

Definition at line 66 of file debug_master.v.

|

Signal |

Definition at line 67 of file debug_master.v.

|

Signal |

Definition at line 68 of file debug_master.v.

|

Signal |

Definition at line 69 of file debug_master.v.

|

Signal |

Definition at line 70 of file debug_master.v.

|

Signal |

Definition at line 71 of file debug_master.v.

|

Signal |

Definition at line 72 of file debug_master.v.

|

Signal |

Definition at line 73 of file debug_master.v.

|

Signal |

Definition at line 74 of file debug_master.v.

|

Signal |

Definition at line 75 of file debug_master.v.

|

Signal |

Definition at line 77 of file debug_master.v.

|

Signal |

Definition at line 78 of file debug_master.v.

|

Signal |

Definition at line 79 of file debug_master.v.

|

Signal |

Definition at line 80 of file debug_master.v.

|

Signal |

Definition at line 81 of file debug_master.v.

|

Module Instance |

Definition at line 119 of file debug_master.v.

|

Module Instance |

Definition at line 108 of file debug_master.v.

|

Module Instance |

Definition at line 136 of file debug_master.v.

The documentation for this Module was generated from the following files:

- util_modules/debug_master.v