csconvert_jp4 Module Reference

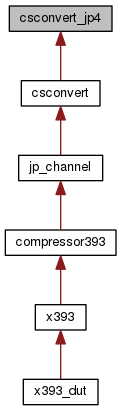

Inheritance diagram for csconvert_jp4:

Static Public Member Functions |

Always Constructs | |

| ALWAYS_132 | ( clk ) |

Public Attributes |

Inputs | |

| en | |

| clk | |

| din | [ 7 : 0 ] |

| pre_first_in | |

Outputs | |

| y_out | [ 7 : 0 ] |

| yaddr | [ 7 : 0 ] |

| ywe | |

| pre_first_out | |

Signals | |

| wire | pre_first_out |

| wire[ 7 : 0 ] | y_out |

| reg[ 7 : 0 ] | yaddr_cntr |

| reg | ywe |

| wire[ 7 : 0 ] | yaddr |

Detailed Description

Definition at line 41 of file csconvert_jp4.v.

Member Function Documentation

|

Always Construct |

Definition at line 64 of file csconvert_jp4.v.

Member Data Documentation

|

Input |

Definition at line 50 of file csconvert_jp4.v.

|

Input |

Definition at line 51 of file csconvert_jp4.v.

|

Input |

Definition at line 52 of file csconvert_jp4.v.

|

Input |

Definition at line 53 of file csconvert_jp4.v.

|

Output |

Definition at line 54 of file csconvert_jp4.v.

|

Output |

Definition at line 55 of file csconvert_jp4.v.

|

Output |

Definition at line 56 of file csconvert_jp4.v.

|

Output |

Definition at line 57 of file csconvert_jp4.v.

|

Signal |

Definition at line 59 of file csconvert_jp4.v.

|

Signal |

Definition at line 60 of file csconvert_jp4.v.

|

Signal |

Definition at line 61 of file csconvert_jp4.v.

|

Signal |

Definition at line 62 of file csconvert_jp4.v.

|

Signal |

Definition at line 63 of file csconvert_jp4.v.

The documentation for this Module was generated from the following files:

- compressor_jp/csconvert_jp4.v